# **BRNO UNIVERSITY OF TECHNOLOGY**

VYSOKÉ UČENÍ TECHNICKÉ V BRNĚ

# FACULTY OF ELECTRICAL ENGINEERING AND COMMUNICATION

FAKULTA ELEKTROTECHNIKY A KOMUNIKAČNÍCH TECHNOLOGIÍ

### DEPARTMENT OF MICROELECTRONICS

ÚSTAV MIKROELEKTRONIKY

# PROGRESS TOWARD THE DEVELOPMENT OF SINGLE NANOWIRE-BASED ARRAYS FOR GAS SENSING APPLICATIONS

POKROK VE VÝVOJI SNÍMACÍCH POLÍ ZALOŽENÝCH NA JEDNOM NANODRÁTU A JEJICH VYUŽITÍ V OBLASTI DETEKCE PLYNŮ

### **DOCTORAL THESIS**

DIZERTAČNÍ PRÁCE

AUTHOR Ing. Ondřej Chmela

**AUTOR PRÁCE**

SUPERVISOR Assoc. Prof. Jaromír Hubálek

ŠKOLITEL

CO-SUPERVISOR Dr. Stella Vallejos Vargas

**ŠKOLITEL SPECIALISTA**

**BRNO 2019**

### **Abstract**

This thesis presents the development of silicon-based platforms for selective integration of semiconducting metal oxide (MOX) nanostructures and their use as highly sensitive and selective elements for the detection of gas analytes in prospective mobile devices. Semiconducting MOX nanostructures, for instance nanowires, have proved better gas sensing properties including sensitivity, stability and to a certain extent also selectivity as compared to their bulk counterparts. The use of single (or few) nanowire structures connected in parallel has also shown to be the ideal architecture to achieve well-defined conduction channel easy to modulate by the gas-solid interactions. However, yet current methods for the integration of single nanowire structures in functional devices represent a technological challenge, with most of the methods needing the assistance of techniques, such as focused-ion beam (FIB), which restricts the scalability of the process and increases the cost and time of fabrication. In this context, this work is focused on the search and optimization of technological processes to fabricate gas sensing systems based on arrays of single semiconducting nanowires.

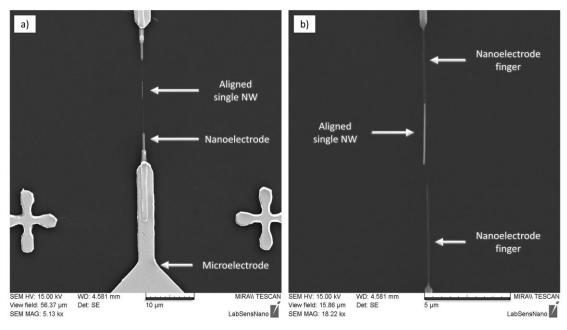

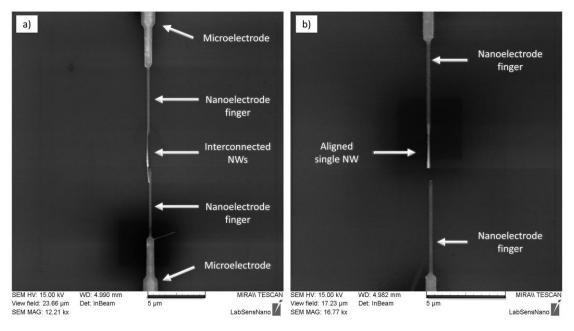

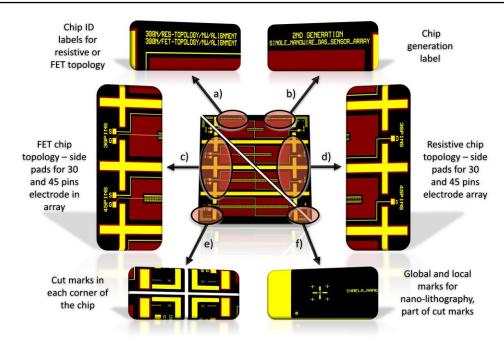

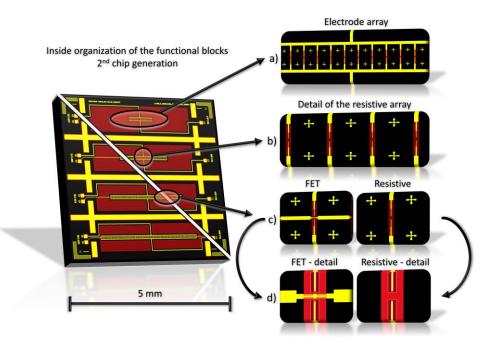

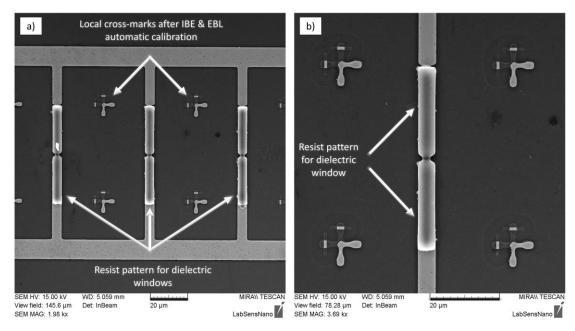

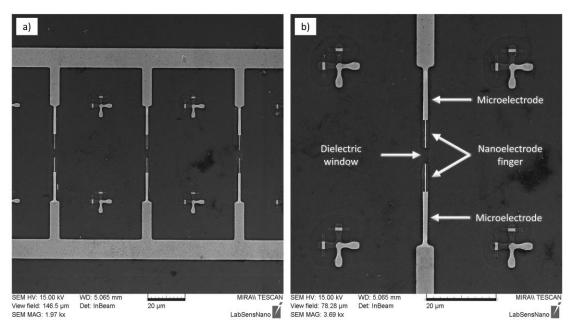

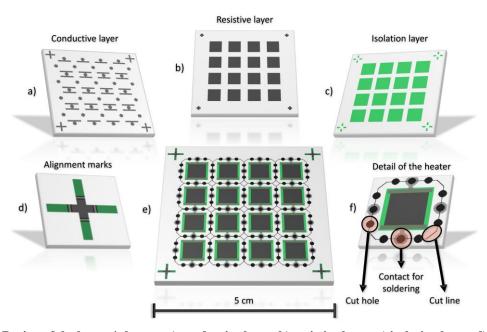

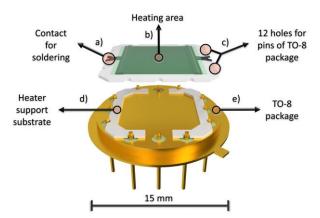

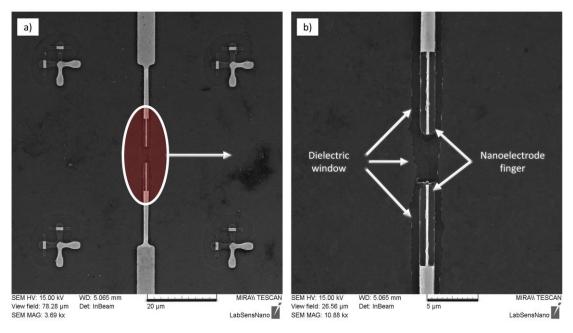

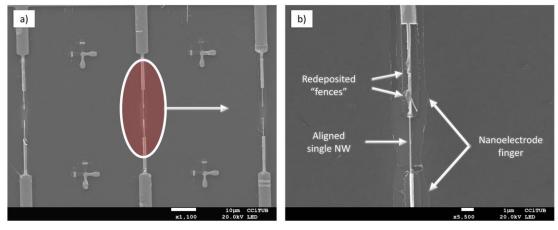

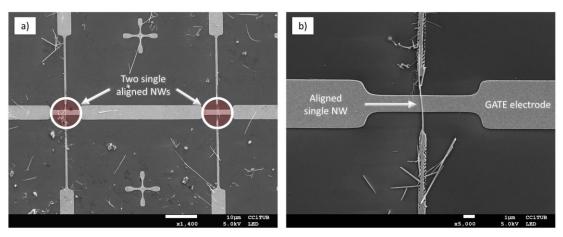

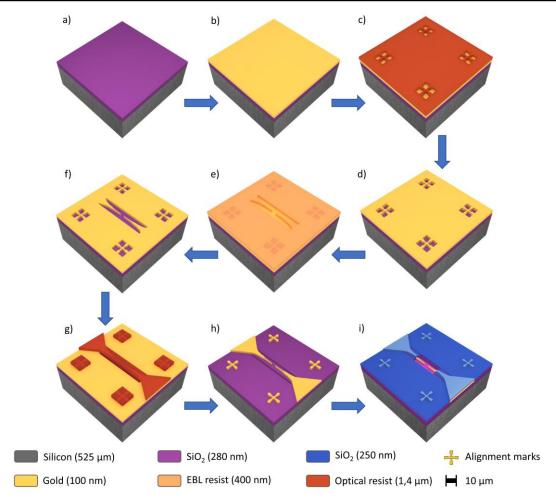

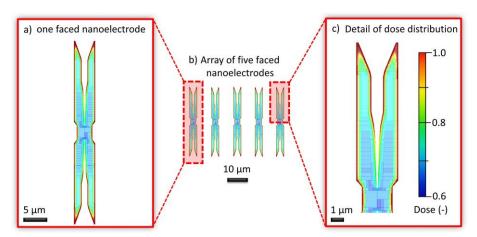

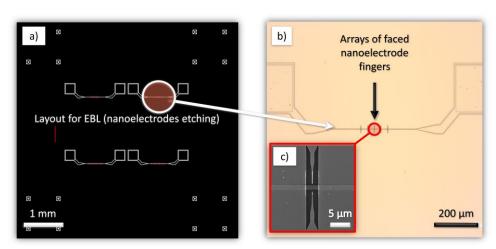

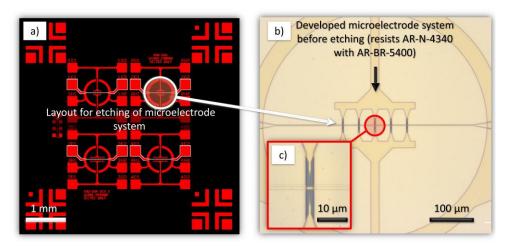

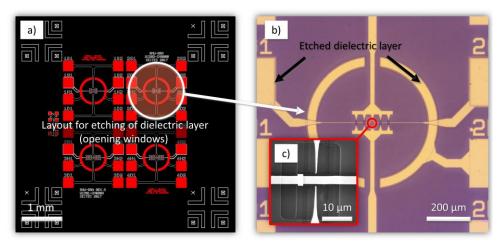

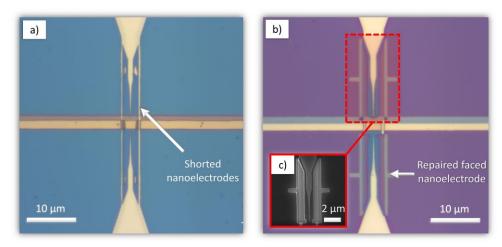

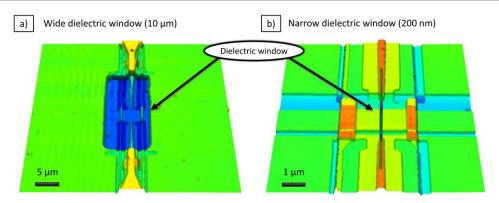

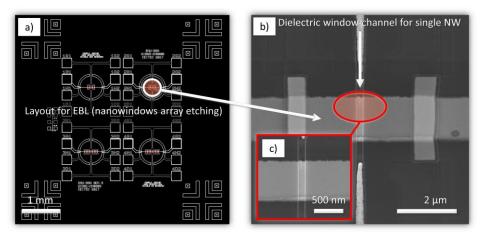

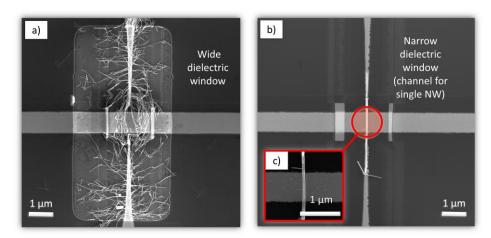

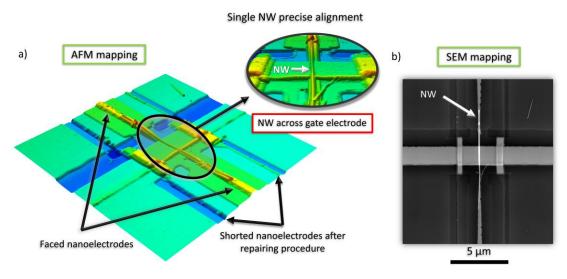

In this thesis, three versions of electrode platforms were developed for the selective integration of single gas-sensitive metal oxide nanowires. State-of-the-art multistep throughput fabrication techniques, as well as electron-beam lithography (nanofabrication), were used as crucial fabrication technologies allowing the development of arrays with faced nanoelectrodes and other functional nanostructures. Results show the fabrication of electrode platform with faced nanoelectrodes (100 - 300 nm width) framed in narrow dielectric windows close to the nanowire diameter (100 - 200 nm approx.). These nanoelectrodes were used as both mechanical support to align the single nanowire, and electrical contacts to measure the electrical change along the nanowire during gas detection. Results also include the optimization of techniques for removal and redeposition of nanowires to achieve single nanowire interconnections in the array of parallel electrodes using an alternating electric field as a simple and effective technique for nanowires alignment (dielectrophoresis).

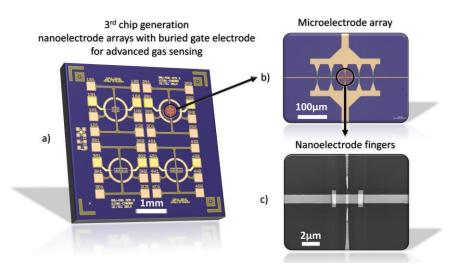

The validation of these systems toward various gaseous species (oxidizing and reducing gases) was performed using non-functionalized and Pt-functionalized WO<sub>3</sub> nanowires synthesized by aerosol-assisted chemical vapor deposition (AACVD) and backside ceramic heaters (with the operating temperature at 250 °C) assembled on TO-8 package. The sensing parameters of such systems showed better sensing responses in resistive regime to nitrogen dioxide (NO<sub>2</sub>) and ethanol (EtOH) than their counterparts based on multiple nanowire-based films. The last version of gas sensing systems developed in this thesis (described as third chip generation) includes a third insulated electrode buried under the gas sensitive nanowire for enhanced gas sensing regime. Gas sensing tests of this system to hydrogen (H<sub>2</sub>) and nitrogen dioxide (NO<sub>2</sub>) corroborated the enhanced functionality of these systems and the modulation of sensor response by applying external electrical stimuli on the buried electrode.

### Keywords

Electrode platform, nanoelectrodes, array of single nanowires, nanowire alignment, sensing system, gas detection.

### **Abstrakt**

Tato práce se zabývá vývojem platforem na bázi křemíkového substrátu pro selektivní integraci polovodivých nanostruktur oxidu kovu (MOX) a jejich použití v perspektivních mobilních zařízeních jako vysoce citlivé a selektivní prvky pro detekci analytů plynů. Polovodičové nanostruktury MOX, například nanodráty, prokázaly lepší schopnosti pro snímání plynů včetně citlivosti, stability a do jisté míry také selektivity, ve srovnání s jejich protějšky na bázi vrstev. Rovněž použití jednoho (nebo několika) nanodrátů zapojených paralelně se ukázalo jako ideální architektura pro dosažení dobře definovaného vodivého kanálu snadno modulovatelného interakcemi na přechodu plynná-pevná látka. Dosavadní způsoby integrace struktur na bázi jednoho nanodrátu do funkčních zařízení však stále představují technologickou výzvu, protože většina metod vyžaduje asistenci technik, jako je soustředěný iontový paprsek (FIB), který omezuje škálovatelnost a zvyšuje náklady a čas výroby. V této souvislosti je práce zaměřena na optimalizaci technologických procesů pro výrobu systémů založených na elektrodových polích s jedním polovodivým nanodrátem.

V této práci byly vyvinuty tři verze elektrodových platforem pro selektivní integraci jednoho nanodrátu z MOX materiálu citlivého na plyn. Jako klíčové technologie výroby byly použity nejmodernější vícestupňové výrobní postupy a litografie s využitím elektronového paprsku (nanofabrikace), které umožňují vývoj elektrodových polí s přímými nanoelektrodami, ale i dalších funkčních nanostruktur. Výsledky demonstrují výrobu elektrodové platformy s přímými nanoelektrodami (šířky 100–300 nm), na kterých se nachází úzká dielektrická okna s šířkou blízké průměru nanodrátu (přibližně 100–200 nm). Tyto nanoelektrody byly použity jako mechanická podpora pro zarovnání jednoho nanodrátu a rovněž jako elektrické kontakty pro měření elektrické změny nanodrátu během detekování plynu. Výsledky také zahrnují optimalizaci technik pro odstraňování a opětovné nanášení nanodrátů pro dosažení jedno nanodrátových propojení v poli paralelních elektrod pomocí střídavého elektrického pole jako jednoduché a účinné metody pro zarovnávání nanodrátů (dielektroforéza).

Ověření těchto systémů vůči různým plynným látkám (oxidačním a redukčním plynům) bylo provedeno za použití nefunkcionalizovaných a Pt-funkcionalizovaných WO3 nanodrátů syntetizovaných pomocí aerosolové chemické depozice par (AACVD) a topného prvku na bázi tlusté vrstvy na korundové keramice (s provozní teplotou 250 °C), sestaveného spolu s elektrodovou platformou na pouzdru TO-8. Snímací vlastnosti takových systémů vykazovaly lepší citlivost v odporovém režimu na oxid dusičitý (NO2) a ethanol (EtOH) než jejich protějšky využívající nanodrátových filmů. Poslední verze systému pro snímání plynu vyvinutého v této práci (popsaná jako třetí generace čipů) obsahuje třetí izolovanou elektrodu zabudovanou (utopenou) pod citlivým nanodrátem pro zvýšení detekční schopnosti snímání plynu. Testy odezvy na vodík (H2) a oxid dusičitý (NO2) potvrdily zvýšenou funkčnost tohoto systému modulující odezvu senzoru pomocí externího elektrického napětí na utopené elektrodě.

### Klíčová slova

Platforma s elektrodovým polem, nanoelektrody, pole založené na jednom nanodrátu, zarovnávání nanodrátů, sensitivní systém, detekce plynů.

# Bibliographic citation CHMELA, O. Progress toward the development of single nanowire-based arrays for gas sensing applications. Brno, 2020. Available: https://www.vutbr.cz/studenti/zav-prace/detail/122581. Doctoral thesis. Brno university of technology, Faculty of electrical engineering and communication, 2020. 199 p. Supervisor Assoc. Prof. Jaromír Hubálek, and co-supervisor Dr. Stella Vallejos Vargas.

| Declaration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I declare that I am the author of the doctoral thesis "Progress in the development of single nanowire-based for gas sensing applications" under the supervision of Assoc. Prof. Jaromín Hubálek, and Dr. Stella Vallejos Vargas, using specialized literature and other information sources, all of which are cited in this work and listed in the bibliography at the end of the work.                                                                                                        |

| As the author of this dissertation, I further declare that in connection with the creation of this dissertation I have not infringed the copyrights of third parties, in particular, I have not infringed illegally on foreign personal rights, and I am fully aware of the consequences of violating Section § 11 and subsequent Copyright Act No. 121/2000 Coll., including possible criminal consequences arising from the provisions of Section § 152 the Criminal Code No. 140/1961 Coll. |

| Brno, 12 <sup>th</sup> September 2019                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Dino, 12 Deptember 2017                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Ing. Ondřej Chmela, author

### Acknowledgments

First of all, I would like to express my sincere gratitude and appreciation to all the people who have supported me in any way during the development of this work. Special thanks to my supervisors Assoc. Prof. Jaromír Hubálek and Dr. Stella Vallejos Vargas for giving me the opportunity to do my doctoral thesis under their leadership. I am deeply grateful to Assoc. Prof. Jaromír Hubálek for providing the support of his research group "LabSensNano" with an excellent scientific background that helped me to realize the goals of this work. I extend the word of appreciation to Dr. Stella Vallejos Vargas for her valuable scientific suggestions and methodological guidance, but also her endless and helpful support during this doctoral work. Without her patience, friendly approach and her confidence in me, it would have been tough to pursue this research.

My thanks also to colleagues from University of Barcelona (MIND & IN2UB), namely, Prof. Albert Romano-Rodriguez, Jordi Samà Monsonís, and Guillem Domènech-Gil, for the pleasant help and collaboration that accompanied my internships in Barcelona during my doctoral study. Personal thanks to Alexandra, Matteo, Maga, Samuel, Guillem, Pepe & Natálka Mizerovi, for their kind love, friendship, and endless support during my days in Barcelona; my deepest gratitude to all of you for making me feel like I have a second family.

My sincere thanks to Jakub Sadílek, for his excellent guidance and collaboration in sharing his broad knowledge and experience in the micro/nanofabrication. Moreover, I would like to thank my colleagues Dr. Zdeněk Pytlíček and Dr. Jaromír Žák, for all the support, help and advice during my Ph.D. study. Also, my heartfelt gratitude to my friends Jakub S., Alexandr O., René M., Pavel H., Tomáš T., and Jan R., for their unconditional support and encouragement during these difficult years.

Thank you, my friends!

Finally, I would also like to thank my lovely parents, Jiří & Ivanka Chmelovi, and loved ones for their patience and psychological support not only in writing this dissertation but also during my long studies at Brno University of Technology. I want to say I am truly sorry for the time I was not with them, but with this work. Hope, it was worth it.

### This work was supported by the following projects:

- New types of electronic circuits and sensors for specific applications, FEKT-S-14-2300,

- Utilization of novel findings in micro and nanotechnologies for complex electronic circuits and sensor applications, FEKT-S-17-3934,

- Surface modified nanowires for selective detection of volatile organic compounds (NoWSens), GAČR 17-16531S.

Faculty of Electrical Engineering and Communication

Brno University of Technology Technicka 12, CZ-61600 Brno, Czechia

http://www.six.feec.vutbr.cz

The research described in this dissertation thesis has been done in laboratories supported by Sensor, Information and Communication Systems Research Centre (SIX) project; registration number CZ.1.05/2.1.00/03.0072 Operational Program Research and Development for Innovation (operační program Výzkum a vývoj pro inovace).

Středoevropský technologický institut BRNO | ČESKÁ REPUBLIKA

This work was carried out with the support of CEITEC -Central European Institute of Technology with intensive help of research infrastructure financed by project CZ.1.05/1.1.00/02.0068 from European Development Fund.

Part of the work was carried out with the support of CEITEC Nano Research Infrastructure (ID LM2015041, MEYS CR, 2016-2019), CEITEC Brno University of Technology.

"Člověk přišel na svět proto, aby tady byl, pracoval a žil. Jen moudrý se snaží náš svět postrčit dál, posunout výš. A jen vůl mu v tom brání."

"Human came into the world to be here, work and live. Only the wise seek to push our world further, to move higher. And only the ox stands in his way."

Jan Werich

# **Table of contents**

| ln | troduction, motivation, and aims of the thesis                                            | 13 |

|----|-------------------------------------------------------------------------------------------|----|

|    | Human health  Ecosystem and climate changes  Economic and cultural impacts                | 13 |

|    | Motivation                                                                                | 14 |

|    | Aims of the dissertation                                                                  |    |

|    | Scientific contribution                                                                   |    |

|    | Dissertation structure                                                                    |    |

|    | Dissertation structure                                                                    | 10 |

| 1  | State of the art                                                                          | 19 |

|    | 1.1 Classification and characteristic parameters of gas sensors                           | 19 |

|    | 1.2 Solid-state chemical sensors – metal oxide based gas sensors                          | 21 |

|    | 1.2.1 Working principle summary of metal oxide gas sensors                                | 24 |

|    | 1.2.2 Receptor function – gas-solid interactions                                          | 25 |

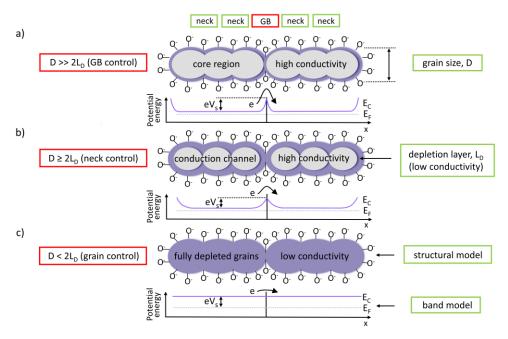

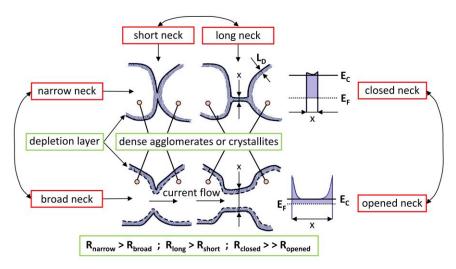

|    | 1.2.3 Transducer function – charge transfer and electrical conductivity via grains of MOX | 33 |

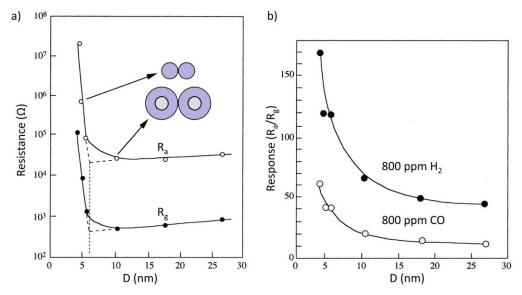

|    | 1.2.4 Effect of grain size and crystalline quality                                        | 36 |

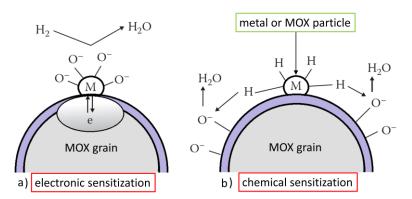

|    | 1.2.5 Effect of surface functionalization by noble metals or MOX particles                | 40 |

|    | 1.3 Nanosensors based on one-dimensional nanowires structures                             | 44 |

|    | 1.3.1 Nanowires synthesis and device fabrication approaches                               |    |

|    | 1.3.2 Effect of nanocrystals morphology on gas sensing properties                         |    |

|    | 1.3.3 The current approach in gas sensing using multiple nanowire-based structures        |    |

|    |                                                                                           |    |

| 2  | Fabrication and development techniques                                                    | 61 |

|    | 2.1 Substrate cleaning and surface preparation before lithography                         | 61 |

|    | 2.1.1 Wet-chemical treatment                                                              |    |

|    | 2.1.2 Oxygen plasma ashing treatment                                                      | 62 |

|    | 2.1.3 Lithography process chemistry                                                       |    |

|    | 2.1.4 Applying and developing resist                                                      |    |

|    | 2.2 Software for the chip design and lithography software for exposure optimization       | 65 |

|    | 2.2.1 Design editor and viewer for the chip layout                                        |    |

|    | 2.2.2 Advanced design optimization tools                                                  |    |

|    | z.z.z Advanced design optimization tools                                                  | 65 |

|    | 2.3 Pattern transfer lithography techniques                                               | 66 |

|    | 2.3.1 Direct-write laser photolithography – maskless lithography                          | 67 |

|    | 2.3.2 Contact and proximity photolithography – through-mask lithography                   | 67 |

|    | 2.3.3 Electron-beam lithography                                                           | 68 |

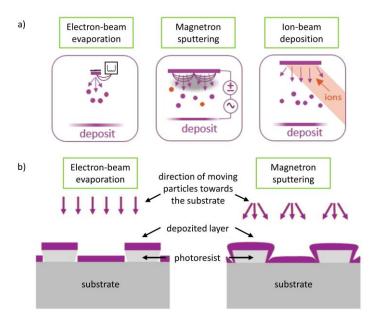

|    | 2.4 Physical vapor deposition techniques                                                  | 69 |

|    | 2.4.1 Ion-beam-assisted deposition and magnetron sputtering                               |    |

|    | 2.4.2 E-beam evaporation                                                                  |    |

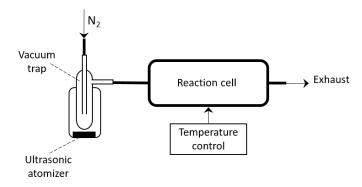

|    | 2.5 Chemical vapor deposition techniques                                                  | 70 |

|    |                                                                                           |    |

|    | 2.5.1 Atomic layer deposition                                                             |    |

|    | 2.5.2 Aerosol-assisted chemical vapor deposition – NWs fabrication                        |    |

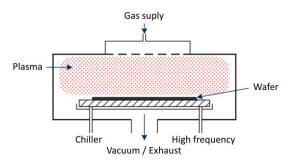

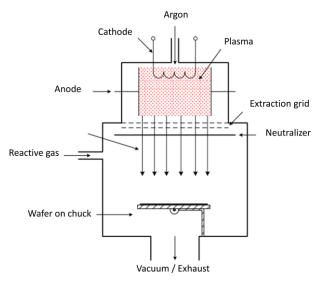

|    | 2.6 Etching techniques                                                                    | 72 |

|    | 2.6.1 Wet etching procedures                                                              |    |

|    | 2.6.2 Reactive-ion etching                                                                |    |

|    | 2.6.3 Ion-beam etching                                                                    | 73 |

|    | 2.7 Measurement, characterization and inspection techniques                               | 74 |

|    | 2.7.1 Surface contact profilometry of objects down to 1 µm                                |    |

|    | 1 / / F:                                                                                  | _  |

|   |      | 2.7.2 Scanning probe microscopy of objects smaller than 1 μm                                        |      |

|---|------|-----------------------------------------------------------------------------------------------------|------|

|   |      | 2.7.3 Spectroscopic reflectometry for thickness measurement of thin films                           |      |

|   |      | 2.7.4 Optical microscopy inspection – microscale imaging                                            |      |

|   |      | 2.7.5 Scanning electron microscopy inspection – nanoscale imaging and analysis                      |      |

|   |      | 2.7.6 Electrical characterization and measurements                                                  | /6   |

|   | 2.8  | Packaging techniques                                                                                | 77   |

|   |      | 2.8.1 Wafer dicing process                                                                          | 77   |

|   |      | 2.8.2 Wire bonding – electrical interconnection from chip to package                                | 77   |

|   |      | 2.8.3 Nanowires processing techniques and assembly using dielectrophoresis                          | 78   |

|   |      |                                                                                                     |      |

| 3 | Firs | st chip generation: Microelectrode array system for nanowires integration using                     |      |

|   | die  | lectrophoresis technique                                                                            | . 79 |

|   | 2.4  |                                                                                                     | -00  |

|   | 3.1  | Experimental and methods                                                                            |      |

|   |      | 3.1.1 Nanowires preparation, removal and redeposition for evaluation of dimensional properties.     |      |

|   |      | 3.1.2 Design requirements of the functional blocks of the microelectrode system                     |      |

|   |      | 3.1.3 Fabrication of the microelectrode array system using wet etching process                      |      |

|   |      | 3.1.4 Nanowires redeposition and integration process using dielectrophoresis                        | 87   |

|   | 3.2  | Results and discussion                                                                              | 88   |

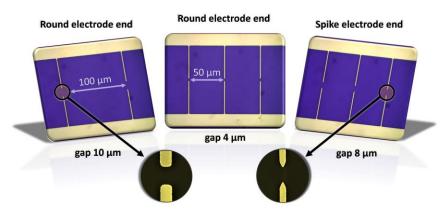

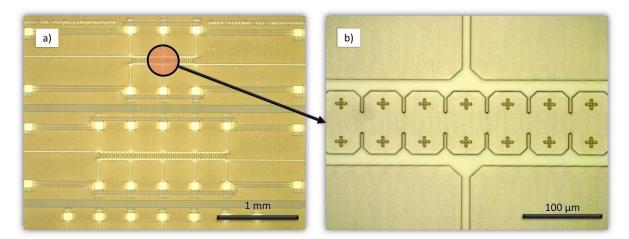

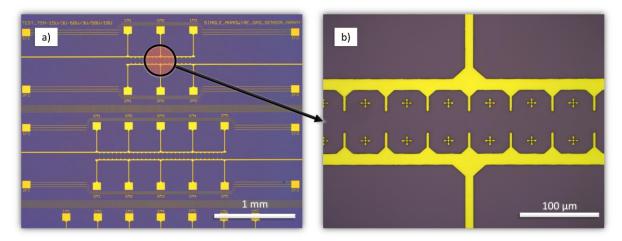

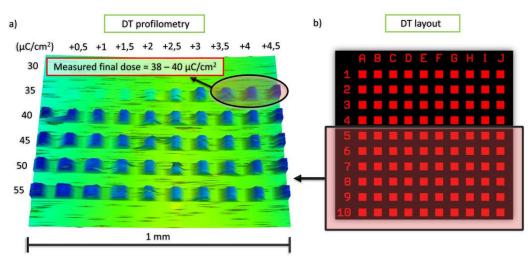

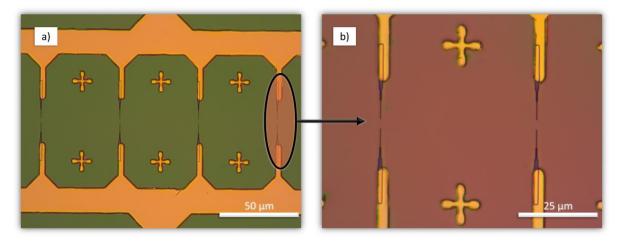

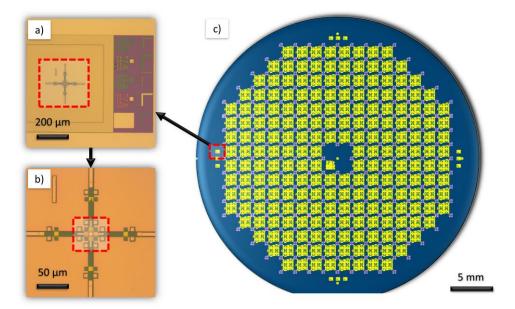

|   |      | 3.2.1 Fabricated test chips with microelectrode arrays for NWs alignment                            | 88   |

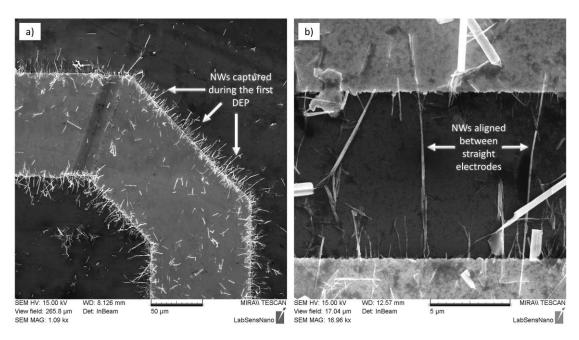

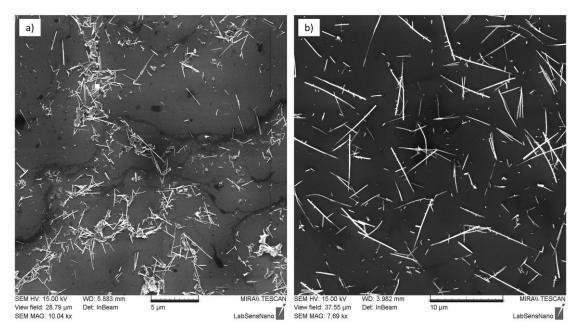

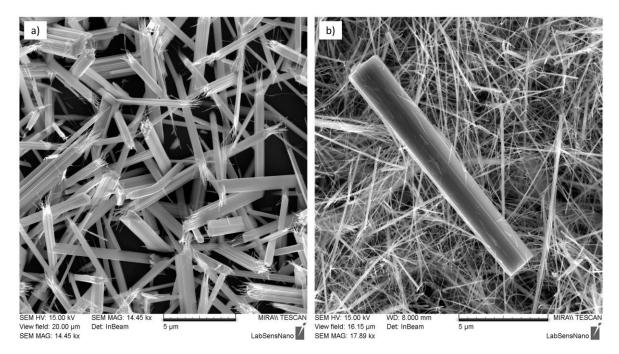

|   |      | 3.2.2 Optimization of nanowires removal, redeposition and integration process                       | 90   |

|   | 22   | Summary                                                                                             | 07   |

|   | 3.3  | Summary                                                                                             | 97   |

| 1 | Soc  | ond chip generation: Nanoelectrode arrays platform for parallel alignment of sing                   | ·lo  |

| - |      |                                                                                                     |      |

|   | nar  | nowires using for gas detection                                                                     | . 98 |

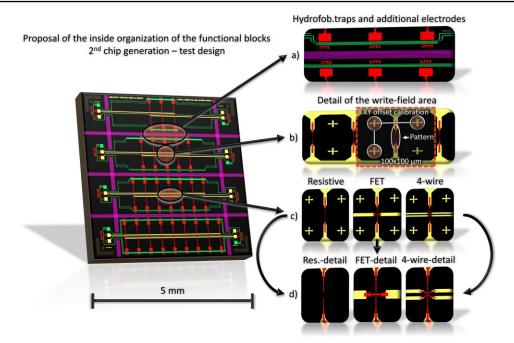

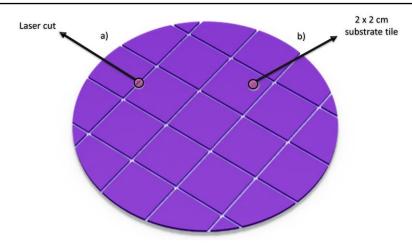

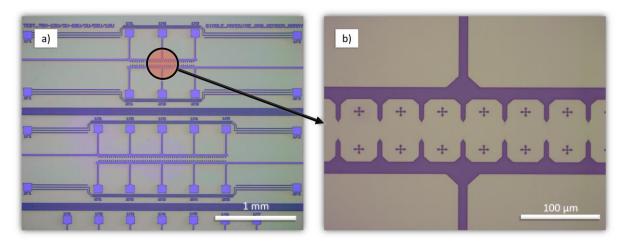

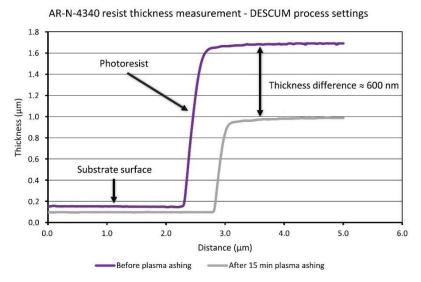

|   | 4.1  | Experimental and methods – part I                                                                   | 99   |

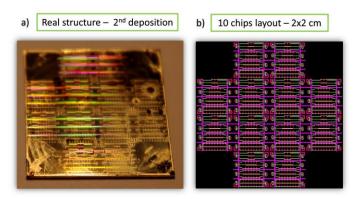

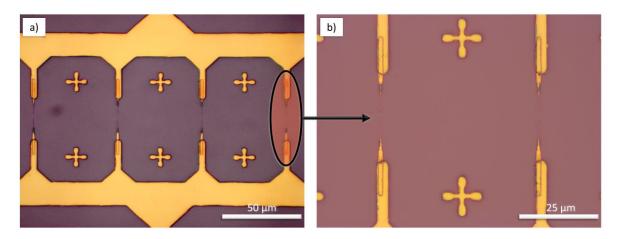

|   |      | 4.1.1 Fabrication of nanoelectrode array test structure on 2x2 cm substrate using lift-off process  | 99   |

|   | 4.2  | Desults and discussion worth                                                                        | 100  |

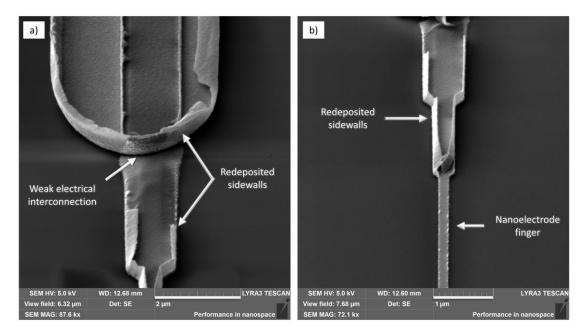

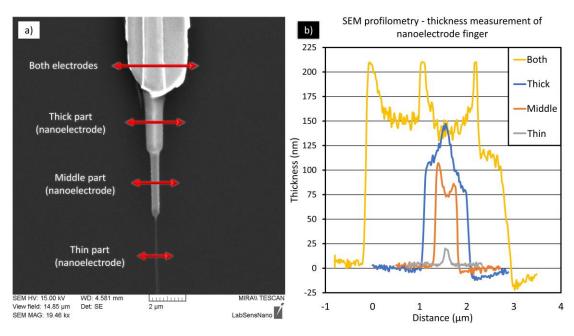

|   | 4.2  | Results and discussion – part I                                                                     | 108  |

|   | 4.3  | Experimental and methods – part II                                                                  | 112  |

|   |      | 4.3.1 Design concept and specification of the nanoelectrode arrays and other functional blocks on   | the  |

|   |      | chip                                                                                                | 112  |

|   |      | 4.3.2 Fabrication of optimized nanoelectrode array structure using etch-back process (preferred     |      |

|   |      | process)                                                                                            | 116  |

|   |      | 4.3.3 Design and fabrication of heating elements for gas testing                                    |      |

|   |      | 4.3.4 Nanowires integration and sensor assembly procedure                                           |      |

|   |      | 4.3.5 Nanoelectrode arrays with single aligned NWs in parallel gas tests                            | 122  |

|   | 4.4  | Results and discussion – part II                                                                    | 123  |

|   |      | 4.4.1 The optimized fabrication process of nanoelectrode arrays on 2-inch wafers for gas sensing    |      |

|   |      | applications                                                                                        | 123  |

|   |      | 4.4.2 Heater electrical and temperature characterization                                            |      |

|   |      | 4.4.3 Gas sensing tests                                                                             |      |

|   |      | •                                                                                                   |      |

|   | 4.5  | Summary                                                                                             | 139  |

| _ |      |                                                                                                     |      |

| 5 |      | rd chip generation: Advanced nanoelectrode array platform for enhancing of gas                      |      |

|   | sen  | sing properties based on three electrodes configuration                                             | 141  |

|   | 5 1  | Experimental and methods                                                                            | 1/12 |

|   | J.1  | 5.1.1 Design concept and specification of the advanced nanoelectrode arrays and other functional    |      |

|   |      | blocks on the chip                                                                                  |      |

|   |      | 5.1.2 Fabrication of advanced nanoelectrode array structure with a buried gate electrode using high |      |

|   |      | throughput techniques                                                                               | -    |

|   |      | 5.1.3 Design and fabrication of a TO-8 gas chamber for low-current measurement                      |      |

|   |      |                                                                                                     |      |

|   | 5.2  | Results and discussion                                                                              | 157  |

### Progress toward the development of single nanowire-based arrays for gas sensing applications

| 5.3             | Summary                                               | 169                                                                                                                      |  |  |

|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Ger             | neral conclusions and future perspectives             | 171                                                                                                                      |  |  |

| 6.1             | General conclusions                                   | 171                                                                                                                      |  |  |

|                 |                                                       |                                                                                                                          |  |  |

|                 | 6.1.2 On the sensing performance and characterization | 173                                                                                                                      |  |  |

| 6.2             | Future work                                           | 175                                                                                                                      |  |  |

| t of            | tables                                                | 181                                                                                                                      |  |  |

| t of            | attachments                                           | 181                                                                                                                      |  |  |

| List of figures |                                                       |                                                                                                                          |  |  |

| fere            | nces                                                  | 187                                                                                                                      |  |  |

| rri c           | ulum Vitae                                            | 198                                                                                                                      |  |  |

|                 | Ger<br>6.1<br>6.2<br>t of<br>t of<br>fere             | 5.2.1 Advanced nanoelectrode arrays on 4-inch wafers and optimization of the structural pa for single NW interconnection |  |  |

### Introduction, motivation, and aims of the thesis

Environmental surveillance is still an important topic in the agenda of government enforces agencies, which in the last years have increased their interest in monitoring emissions continuously at the source, with cross-stack instruments designed to detect particular measurands in reasonable well-known background matrix. The efficiently of this approach relies on the availability of gas sensing systems with increased measurement capabilities and decreased overall capital cost for multiple gas detection so that they can cover wider geographical area with a larger network of monitoring stations. Current gas sensing systems, however, do not fulfill all these requirements, and therefore the interest in further technological improvements of these systems. Generally, the deployment of advanced gas sensing elements could contribute to better control of air pollution and thus have an impact in the following areas.

### **Human** health

Air pollution is one of the most significant environmental health risks in Europe and worldwide causing a wide range of diseases (e.g., lung cancer, cardiovascular and respiratory diseases). Also, air pollution has been associated with adverse influences on fertility, pregnancy, newborns, and children. In particular, it has a negative effect on neural development and cognitive abilities, which can lead to low performance at school and later to a lower quality of life [1]. Another diseases (except hearth and lung diseases), which are responsible for cases of premature death attributed to air pollution, are stroke and new-onset type two diabetes in adults [2].

### **Ecosystem and climate changes**

Air pollution also has several environmental impacts on the ecosystems (e.g., vegetation, quality of water). Here are a few pollutants which causing biodiversity loss. For instance, high levels of nitrogen oxides (the sum of nitrogen dioxide (NO<sub>2</sub>) and nitrogen monoxide (NO)), ammonia (NH<sub>3</sub>), Volatile Organic Compounds (VOC) and sulfur dioxide (SO<sub>2</sub>), burden aquagenic and terrestrial ecosystems by excessive quantities of nitrogen and sulfur. This contributes to the acidification of soil, rivers, and lakes.

Also, it is a well-known fact that several air pollutants have an impact on global weather changes. For instance, ground-level ozone (O<sub>3</sub>) formation, formed in the lower part of the atmosphere, methane (CH<sub>4</sub>) or carbon dioxide (CO<sub>2</sub>). All of these pollutants and their increasing tendency of occurrence are a serious worldwide problem. As an example can be used increasing of the methane production(CH<sub>4</sub>), which is characterized as a greenhouse gas (GHG). GHG emissions are presupposed to rise by 50 % in 2050 compared to 2011, and from a global perspective, up to 18% of global GHG emission is accounted to the livestock sector, the dairy cow production, respectively. [3,4]

### **Economic and cultural impacts**

In light of the actual conditions of air pollution, which have the evidential influence on human health, the global climate, and ecosystems, it should also emphasize the potential economic consequences of the deteriorating air conditions in the future. The European Commission estimated that total health-related external costs in 2010 were in the range of EUR 330–940 billion, including direct economic damages of EUR 15 billion from lost workdays, EUR 4 billion from healthcare costs, EUR 3 billion from crop yield loss and EUR 1 billion from damage to buildings. [5]

The Organisation for Economic Co-operation and Development (OECD) projects market costs (e.g., additional health expenditure, forest yield losses) reach about 2% of European gross domestic product (GDP) in 2060, leading to a reduction in capital accumulation and a slowdown in economic growth. Non-market costs (also referred to as welfare costs) are those associated with increased mortality and morbidity (illness-causing, for example, pain and suffering), degradation of air and water quality and consequently ecosystems health, as well as climate change. Globally, air pollution could cause 6 to 9 million of premature deaths a year by 2060 and cost 1% of global GDP (around 2.6 trillion USD annually), as a result of sick days, medical bills and reduced agricultural output. [6]

Indeed, new technologies brought many benefits to our new modern lives. However, they also brought many inconveniences, such as the increase of unwanted global release of air pollutants that will result in enormous costs to cover those environmental and health losses in the next few decades. The consequences are very significant, and there is a need to call for strong policy actions, which need to be supported by the implementation of advanced monitoring technologies for environmental surveillance, restoration, and remediation.

### Motivation

Gas sensing systems are expected to play a notable role in environmental control and monitoring, to secure a better quality of life for the next generations [7,8]. The necessity of gas sensing in different fields (industrial safety, security, environmental surveillance, biomedical, to cite few) has been analyzed previously by the global gas sensor market, which predicts a gas sensor market size of USD 1.82 billion in 2016 and an estimated growth at a CAGR (Compound Annual Growth Rate) of 7.5 % from 2017 to 2025 [9]. Therefore, the fabrication of the new generation of gas sensing systems requires the deployment of advanced techniques and concepts that allow not only for high performance elements, but also for low power consumption miniaturized systems so that they can be integrated in portable or wearable components, as opposed to the current gas sensing technologies in the market [10].

These new characteristics could facilitate the approach of these systems into a human's ordinary life, for example, by means of sensing platform integrated into mobile (portable) devices, such as smartphones. Thus, everybody could have the chance to monitor the actual air

conditions (toxicity of the pollution) and control the areas that could possibly represent a risk. This could also have other effects, as these smart sensors become part of the equipment of our mobile phones so that the data recorded can be potentially used for real-time detection and shared with other users to inform the current air situation in their vicinity. Online health monitoring from exhaled breath is another possible application, which could also bring positive benefits for preventive medicine [11]. All this would allow to ordinary people to have clear records based on evidence from millions of mobile sensors in their hands that the environment in their city, village, or region, is dangerous to their health. Thus, it can increase the pressure on politicians to do fundamental changes in the policies.

In this context, during the last decades, many researchers have focussed on different aspects that involve gas sensing technologies. Thus, a variety of sensors, systems, and technologies have been developed for sensing and monitoring gases or vapors. Pellistors, electrochemical, optical, and thick film metal oxides (MOX) are the most famous gas sensing devices; however, these technologies do not accomplish the above-mentioned conditions of size, cost, and performances at low concentration levels. As an alternative, gas sensor based on nanomaterials (particularly semiconducting oxides) and micro/nanotechnologies are good candidates for this application as they can allow for miniaturized gas detectors. The miniaturization of devices reduces material consumption in device manufacture and reduces power consumption in device operation. Sensors miniaturization also offers faster response times and lower detection limits than traditional commercial ceramic-based devices, enabling sensors to be deployed on-site and making real-time detection possible.

One-dimensional (1D) semiconducting metal-oxide (MOX) nanostructures in the form of nanowires, nanorods or nanobelts have demonstrated to play a significant role in the functional properties of gas sensing systems, typically improving their performance, as opposed to bulk MOX. For instance, 1D MOX have demonstrated to improve parameters, such as the sensitivity and stability of the sensing element, and also, to a certain extent, the selectivity [12] [13]. It has also been demonstrated that gas sensors based on a single (or few) nanowire structures connected in parallel are the ideal architecture to achieve well-defined conduction channel easy to modulate by external stimuli (e.g., gaseous molecules) [12,14-17]. However, yet current methods for the integration of single nanowire structures in functional devices represent a technological challenge, with most of the methods needing the assistance of techniques, such as focus ion beam (FIB), which restricts the scalability of the process and increases the cost and time of fabrication [18,19]. In this context, this work is focussed on the search and optimization of technological processes to fabricate gas sensing systems based on arrays of single semiconducting nanowires.

### Aims of the dissertation

To address the fabrication of single nanowire-based system this thesis is centered in two general aims (1) the development of platforms provided of nanoelectrode arrays for the selective integration of single gas-sensitive metal oxide nanowires and (2) the validation of these platforms toward various gaseous species. To achieve these general aims, it was necessary to face several scientific and technological issues; therefore, the specific aims were set to provide systematic feedback at each step and thus improve the whole system fabrication process. The specific aims and the most relevant tasks carry out to reach these aims are summarized below.

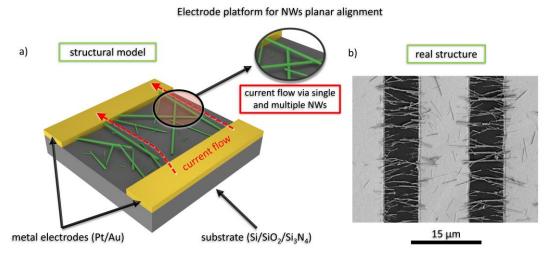

- 1. Determination and optimization of nanowires processing techniques this aim was focused on finding the appropriate techniques for the removal (from a basic substrate) of the as-deposited AACVD nanowires. The transfer, positioning, and integration of nanowires into the prefabricated electrode arrays using approaches that provide large-scale and easier processability have also been selected and optimized. The optimization of this process includes the setup of techniques suitable to obtain nanowires without significant disturbance of their length, ready to be transported (redeposited) onto the electrode array and integrated between the electrodes as single structures interconnected in parallel by dielectrophoresis technique.

- 2. Setting of the protocol for the fabrication of electrode arrays to provide mechanical support and electrical connectivity to single nanowires the tasks within this aim dealt with the design and implementation of key processing technologies (particularly lithography and etching processes) for the fabrication of arrays of electrodes on silicon platforms. The designs were adjusted based on the features (length and diameter) of the gassensitive nanowires (previously developed via aerosol-assisted chemical vapor deposition AACVD). Three generations of structures were fabricated within this aim, and each one was redesigned and improved based on the feedback obtained from a previous generation in order to achieve the interconnection of several single nanowires in parallel. The last improved modification includes the introduction of an additional electrode system for gas sensing enhancement. It is worth to mention that the processing fabrication techniques for this aim were adjusted to produce structures in the nanoscale order.

- 3. Assembling of the gas sensing system due to the need for a heating element to activate the gas-sensitive structures, an assembly process was required before the application of the fabricated systems. Therefore, this aim was centered in assembling the electrode arrays platform together with a heater element into a package. This step also included the electrical connection of the elements for their characterization and control (to measure the gas responses and control the heater for the set of temperature).

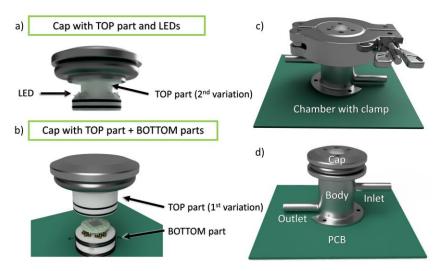

- **4. Development and implementation of the gas characterization system** a system for the validation of the assembled sensing device functionality under exposure to various gases has been developed. The design of the gas testing chamber was addressed to allow the measurement of highly sensitive materials (nanowire), so the design includes (1) maximal electromagnetic interference shielding for low current measurement (high resistance of nanowires), (2) high gas exchange rate, and also (3) minimal adsorption of the chamber.

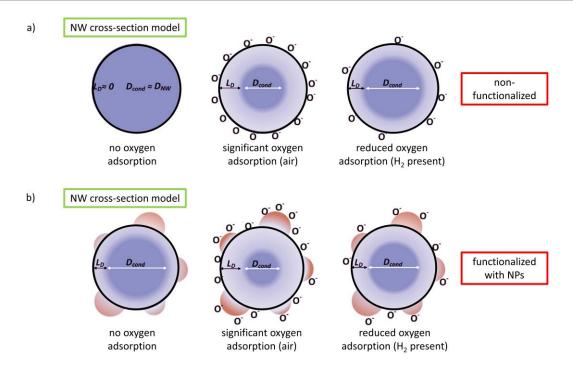

- **5. Gas sensing characterization in resistive mode** the electrode array platform with integrated nanowires have been tested under the exposure to various gases (reducing, oxidizing) and their concentrations. The characterization of the sensing system revealed the parameters for maximum performance, for instance, the appropriate sensing current with good S/N ratio, or the operational temperatures with the highest gas response. Effect of the nanowires (pristine metal oxide) with their surface functionalized by catalytic nanoparticles and its influence on the selectivity and sensitivity of sensing elements have also been examined.

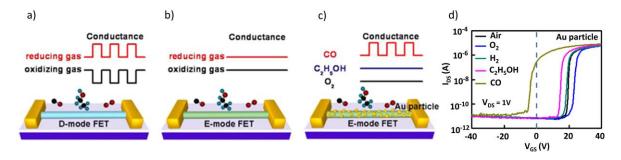

- **6. Gas sensing characterization in enhanced mode** the planar arrangement with the nanowires across the electrodes offers the possibility to control the conductivity of the nanowire channel using an additional (third) electrodes system. The effect of the additional (third) electrode on the gas response, related to the sensitivity and selectivity, has been evaluated in the presence of various gases. This third electrode proved to enhance the sensing properties of the sensing elements due to the applied electric field forces provided to the gas sensitive nanowire.

### Scientific contribution

This dissertation presents a summary of the author's doctoral thesis. The efforts of this work were focussed on developing single-nanowire based gas sensing element. The most relevant aspects developed in this thesis include the methodology for fabricating miniaturized electrode platform systems provided of several arrays with parallel faced electrodes. To this end, several advanced fabrication processes were adjusted and optimized, including the e-beam lithography process for nanoscale fabrication.

The novelty of the developed platforms consists in achieving the parallel connection of various single nanowires in parallel by using electric forces (method) and by modifying the width of the electrode close to the dimensions of the nanowire diameter (structure). This breakthrough opened the door to assemble different types of nanowires in one sensing platform, and thus improve the selectivity of the sensor. This, also contribute to developing other novel structures, described along with the thesis as the third chip generation, which proved the functionality enhancement of planar aligned single NWs interconnected in parallel by external electrical stimuli applied on a third electrode buried under the NWs.

### Dissertation structure

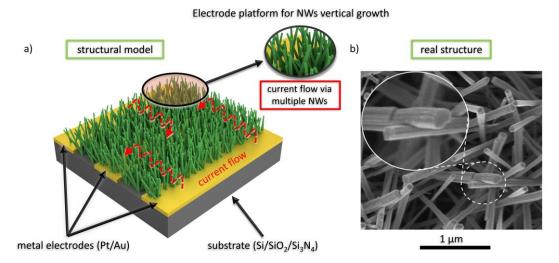

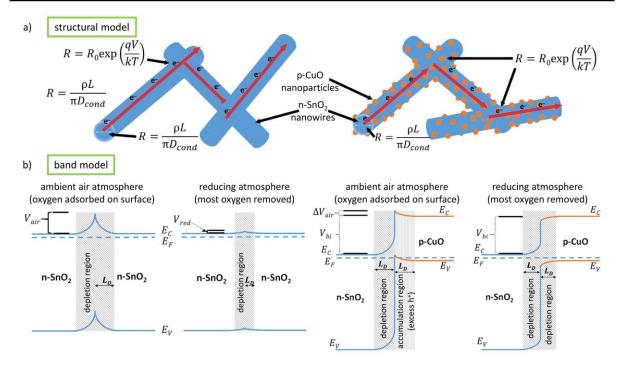

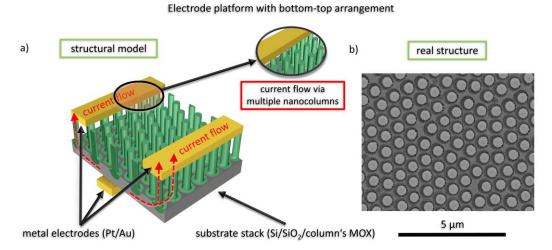

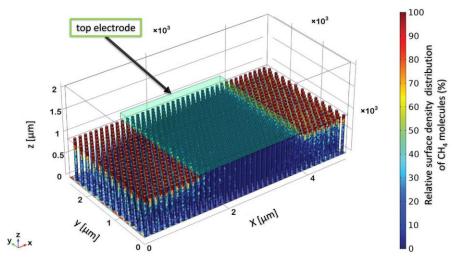

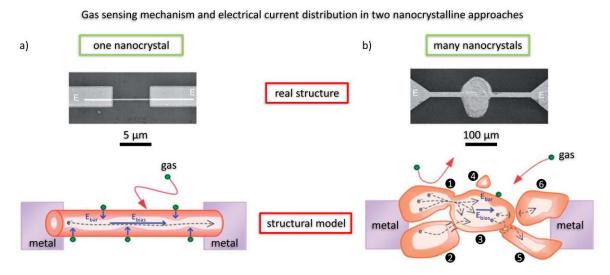

Chapter 1 was dedicated to the theoretical knowledge dealing with solid-state gas sensors based on MOX semiconductors, their working principle with special emphasis on sensing element and the ongoing processes between the sensitive material and adsorbed gas molecules during gas-solid interactions (receptor function), or the mechanism that give rise to the response of gas sensors (transducer function). Thus, influencing effects of the grain size, shape, crystalline quality, or surface functionalization, on the sensor sensitivity and selectivity with the emphasis on single-crystalline materials, were also presented. The last **section (1.3)** of this chapter was addressed to introduce sensing system based on multiple NWs, or single NWs, and their possible electrodes arrangements with particular focus on single NW based platforms and its feasible solution.

The fabrication and development techniques employed during the experimental part of this work were briefly described in **Chapter 2**. Some techniques are compared to each other, for example, to determine the suitability of each technique related to the chosen fabrication approach, as it was the case for the deposition techniques. The e-beam lithography is among the most important techniques used in this work. Without the tune of this process in the current work the required dimensions of the proposed electrode platform solution could not be achieved. The results of the experimental part were presented in **Chapter 3**, **Chapter 4**, and **Chapter 5**, which reflect the degree of maturation both of the designs and processing techniques adjustment. Therefore, these chapters are entitled as first, second and third chip generation. To close the dissertation, the conclusions associated with each objective were summarized (presented) in **Chapter 6**.

### 1 State of the art

### 1.1 Classification and characteristic parameters of gas sensors

A gas sensor is an essential component of an analyzer. In addition to the sensor, the analyzer may contain devices that perform the following functions as sampling, sample transport, signal processing, and data processing. An analyzer may be an essential part of an automated system. The analyzer working according to a sampling plan as a function of time acts as a monitor. [20] Generally, some specific parameters are used in order to evaluate the monitored signal produced by the sensor, which will be explained below.

• Sensitivity and sensor response - the sensitivity is defined as the ratio between the change in the sensor resistance and the change in the gas concentration represented by calibration curve, the slope of the calibration curve, respectively. A more general definition of sensitivity is the ability of a certain method to distinguish between two very close concentration. From this, it can be said that it is related also with sensor response. The maximum relative response of the chemiresistor to the analyte can be expressed as [21]:

$$SR = \frac{\Delta R(\infty)}{R_0} \cdot 100\% = \frac{R_{max} - R_0}{R_0} \cdot 100\%$$

(1.1)

where  $R_0$  is the resistance of the sensor in the absence of the analyte and  $R_{max}$  is the resistance of the sensor in the presence of the analyte. Another frequently used an alternative definition of the sensor response for n-type oxides is:

$$SR = \frac{R_{air}}{R_{aas}}$$

(reducing gas),  $SR = \frac{R_{gas}}{R_{air}}$  (oxidizing gas) (1.2)

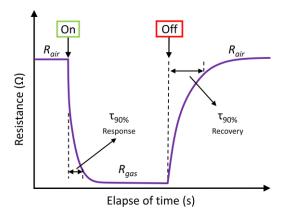

where  $R_{air}$  is the resistance of the sensor in the absence of the analyte and  $R_{gas}$  is the resistance after the subjection to the gas. For oxidizing and reducing gas, in the case of p-type oxides, are these equations reverse. Figure 1 depicts a typical response curve of the gas sensor during gas exposure, where ON determines the time when the flow solution is switched from the buffer, mostly synthetic air, to buffer containing the analyte of interest, OFF is the time when the flow is switched back to the buffer solution without target analyte.

Figure 1. Typical response curve during gas exposure. Adapted from [22].

- The response time and recovery time in gas detection, response time is usually defined as the time taken to achieve 90 % of the final change in resistance following a step change in gas concentration at the sensor and reverse for the recovery time. Often this time is quoted to 50 % or 70 % of the final change. This derives from the response often being very fast initially but having a long-drawn-out tail before the constant value is reached. The shape of the curves can vary from one gas to another. The response time is an important parameter since its value can determine the applicability of the sensor.

- **Selectivity** the data about the different gases makes it possible to determine the selectivity of one gas relative to that of the other gases at any point in the temperature range. The selectivity is usually defined as:

$$Selectivity = \frac{Sensitivity to gas 1}{Sensitivity to gas 2}$$

(1.3)

for equivalent concentrations of both gases, or, sometimes for the concentration of the gases known to be involved in the application of interest. Thus, from the study of sensitivities, an optimum temperature or range of temperatures over which the selectivity is acceptable can be determined.

- **Stability** a gas sensor should be stable in a variable ambient atmosphere. It must also be reversibly unstable in the presence of the gases to be detected. These requirements are difficult to meet simultaneously. Slow changes in the properties of the bulk material or the near-surface region are almost inevitable. Such slow changes, which are the result of changes in the ambient atmosphere or temperature, are called drift.

- Lower Detection Limit is the lowest quantity of an analyte that can be recognized from the absence of the analyte (a blank value) with a stated confidence level which is generally 99%. The detection limit is determined by the sensitivity and noise levels in sensor response. It is often assumed in gas sensor characterization that the limit of detection is reached when the response signal is three times higher than the noise level.

### 1.2 Solid-state chemical sensors – metal oxide based gas sensors

As stated above, the demand for using real-time detection and monitoring is going to be more common in domestic and industrial activities. Generally speaking, a chemical sensor is a device that transforms chemical information into an analytically useful signal (e.g., electrical, optical) for chemical information that can be connected with the concentration of the specific analyte and/or its composition. Traditional analytical instruments, such as mass spectroscopy or chromatography are expensive, complex, bulky and require sample preparation, restricting real-time analyses. In contrast, solid-state chemical sensors have a relatively simple architecture, they are small and can be miniaturized further by using micro/nano technologies for their operation in low-cost portable devices. [23,24]

Nowadays, a large number of different solid-state based gas sensors have been reported due to the productive interdisciplinary science related to solid-state chemistry, physics, biology and so forth. Solid-state gas sensors can be based on a variety of materials, structures, and detection principles. For example, in term of materials, either organic or inorganic materials such as semiconducting metal-oxides or polymers are used as active sensing layers in solid-state gas sensors. Those materials, usually, are in the form of thick/thin films or nanostructures. Also, solid-state gas sensors can work based on various approaches to obtain the desired read-out from the sensitive material. These approaches are generally connected with the physical change used as a detection principle. Thus, typically the electrical conductivity is used as read-out information in chemoresistive gas sensors, mass in piezoelectric sensors (surface acoustic wave, microcantilevers, etc.), optical parameters as reflection, fluorescence or interferometry in optical sensors (fibre optic or thin films), heat or temperature in catalytic gas sensors (Seebeck effect, pellistors) or electromotive force in electrochemical gas sensors. [25]

Solid-state gas sensors have numerous advantages including the possibility to miniaturize the final sensing device using the optimization of silicon micro/nano fabrication techniques, which helps the mass sensor production at low cost. Miniaturization also represents the possibility to get a device with low power consumption, easy integration with electronics and portability. A variety of inorganic materials, typically based on semiconducting metal oxides have proved to detect a wide range of gaseous chemical compounds, but also different reaction capability to them. Actually first gas sensors based on semiconductors were used for detection of explosive gas leakages in residential premises and pollutants inside cars in the 1950s, after the initial publication of gas-sensitive effects on germanium by Brattain and Bardeen [26], then metal oxides were recognized as possible sensitive materials by Heiland et al. [27] and Bielanski et al. [28]. Seiyama et al. published the first report of MOX semiconductor gas sensor in the early 1960s [29]. They manage to develop a new gas detector based on ZnO thin film utilizing the semiconductor catalysis mechanism, where the adsorption and desorption of gaseous compounds cause oxidation and reduction of the surface which evoke a change in the electrical conductivity of the sensing layer. This was a breakthrough advancement which has triggered a new pathway toward the development of new gas sensors based on various MOX materials. Later, Taguchi has patented a gas sensor based on SnO<sub>2</sub> and commercialized it as household gas alarms in 1969. [30]

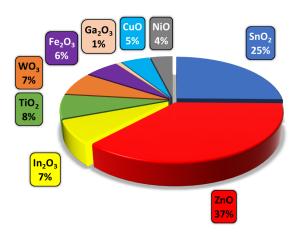

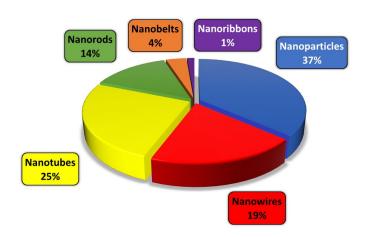

A search in the literature (see pie chart in Figure 2) shows that metal oxides such as SnO<sub>2</sub> or ZnO are the most common materials. Commonly metal oxide based gas sensors work in resistive mode, i.e., sensing the changes produced in the electrical resistance of the material due to the gas-solid interactions characterized by the exchange of electrons. [31,32]

However, the gas sensor based on metal-oxides also have some disadvantages, particularly regarding long-term stability and reproducibility. These undesired problems are related to the sensor functionality during an extended working period. In literature, this is a phenomenon known as "aging effect." There are two types; the first is defined as a drift of the baseline values, which can be conductance or resistivity in air or reference gas. The second is linked to the drift in the sensor response with respect to the calibrated response values. The lack of stability is mainly caused by morphological changes in grains and intergranular boundaries of sensing elements, irreversible reactions with chemical species in the ambient or changes in parameters of the heating element or the electrodes due to aging. [33,34]

Figure 2. Published research on metal-oxide material for gas sensors performed by using the Web of Science database from 1998 to 2018.

Figure 2 also reveals other metal oxides with potential in gas sensings, such as In<sub>2</sub>O<sub>3</sub>, TiO<sub>2</sub>, and WO<sub>3</sub>. In the last few years, these materials have attracted much attention due to strong demand for new sensitive materials seeking, which have been insufficiently studied before and show promissing properties that could allow to develop more selective and sensitive gas sensors. [32,35-37]

Therefore, current efforts in metal oxides gas sensors are devoted to finding novel sensitive materials at the nanoscale and miniaturized transducers of the chemical stimulus in the air into an electrical signal. Miniaturization brings an increasing number of sensor density on a single chip which is taken positively from the energy consumption point of view and more efficient use of materials.

MOX represent a specific class of materials whose are referred to as functional oxides. Their properties are covering the almost entire aspects of material science and physics including metals, semiconductors, isolators, and many others. Moreover, the structures of metal oxides (MOX) are very diverse that there is an infinite quantity of possible new application and phenomena. Such unique characteristics make MOX one of the most used fundamentals of smart devices because the morphology and structure might be controlled precisely. Therefore, deposition and synthesis of the functional, sensitive material is an important step and crucial part due to the fabrication process. Otherwise, the desired material with the required oxide composition is not achieved. [38-40]

Therefore, metal oxides size down to the nanometer scale demonstrate enhanced sensing properties, and in particular novel classes of nanostructures with high-crystallinity structure provide the opportunity to increase gas sensor performance and functionality dramatically. In this context, the literature shows that structured materials as nanotubes and nanoparticles have been studied intensively. Figure 3 displays the pie chart distribution of 1-D metal oxide nanostructures forms used as sensitive material in gas sensors from 1998 until 2018 in the Web of Science database.

Figure 3. Published research related to 1-D nanostructured forms, performed by using the Web of Science database from 1998 to 2018.

This thesis focusses on the use of semiconducting metal oxides (specifically WO<sub>3</sub> nanowires) in sensor applications with the aim to find the best technological solution to enhance and optimize the functionality of these sensitive materials. Generally speaking, research within this cross-connection of technologies based on new nanostructured surfaces such as composite like nanowires decorated with nanoparticles are the subject of our future intention. Modified materials, especially nanowires combined with nanoparticles (NPs) have shown promising properties which can be useful to ensure improved sensitivity or cross selectivity in gas sensing applications. The thesis goes further by joining classical micro and nanotechnological approaches to integrate this material into a miniaturized sensor device with improved performance.

### 1.2.1 Working principle summary of metal oxide gas receptor

In terms of principal components of the sensor, MOX gas receptor (sensor) is effectively a gas-sensitive resistor compose of several functional layers, including the active sensing material (i.e., semiconducting material with a high surface-to-bulk ratio), a heating element (metallic heater track, electrically isolated from the active sensing material, to reach optimal operating temperature) and incorporated electrodes in direct contact with the sensing layer (metallic track in contact with the sensing material to measure the actual ongoing electrical changes).

As stated by Brattain and Bardeen more than five decades ago [26], the electrical conductivity of semiconductor depends on the composition of the gas surrounding a relatively shallow area near to the surface where the reaction is taking place. In this region, the gas-solid interactions lead to charge carrier's density changes by physical adsorption and chemical adsorption. Later, Yamazoe and Shimanoe [41] pointed out that there are many other factors which influence the sensing properties of MOX to measured readout information, respectively. These factors depend not only on the proper selection of a MOX and related method and conditions for fabrication but also crystallite size, contacting geometry between crystals, packing thickness or porosity. Furthermore, the sensing properties of MOX might be largely modified with the loading of foreign substances such as sensitizers, which can enhance the efficiency of catalytic reactions.

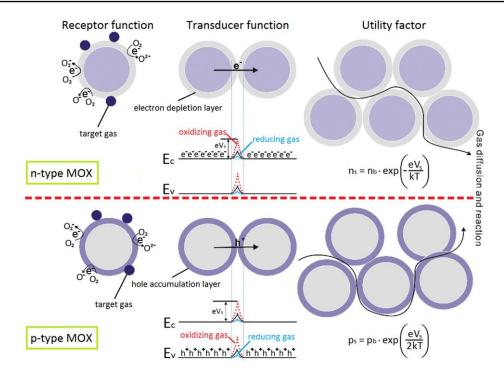

In principle, the readout values of gas sensor depend on key features such as the *receptor* function of the oxide surface that interact with the gas species and the *transducer* ability to transfer the chemical information into an analytically useful signal without attenuation of the response recognized by changes in the electrical conductivity (resistivity). An additional feature includes the penetration depth of target gas into the pores of assembled crystals, this feature is known as a *utility* factor which predicts how the gas response depends on the physical and chemical properties of the microporous structure and target gas.

Accordingly, to the utility factor mentioned above, this feature depends generally on the nature of the structure of the sensitive material. Utility factor can be taken into account in microporous structures or sensitive layers with micro-grains organization, where the diffusion process into the layer is a part of the gas-solid interaction. However, the utility factor may be neglected, for example, when as sensitive material for the gas sensor is used the nanostructured surface, as it is in the case of nanowires, which have the finest crystallography facets and the major gas sensing processes take place on the surface of MOX material. The exact meaning of each function will be specified into details during the following sections.

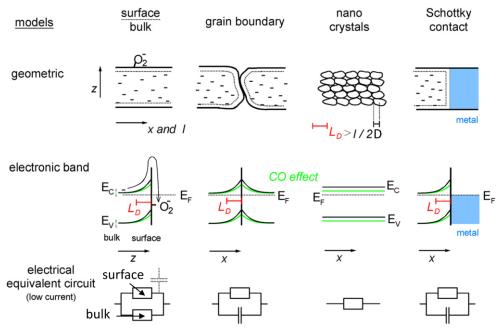

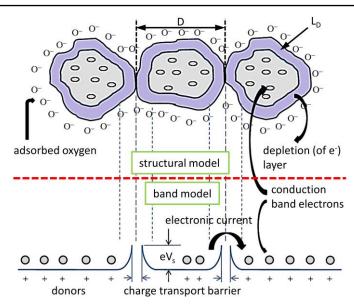

Figure 4. Diagram description of the gas-sensing mechanism and conduction model based on n-type and p-type MOX. Adapted from [42].

Despite facilitating imagining of undergoing processes presented in Figure 4, complex understandings of these phenomena indeed require interdisciplinary knowledge among surface chemistry, semiconductor physics, quantum mechanics and so on. Therefore, in the following section, we will devote our attention to describe the basics of the physical and chemical processes and the mechanism that takes place in metal oxides gas sensors, in order to justify our interest of nanowire-based gas sensors, which will be fabricated and experimentally studied in the subsequent chapters.

### 1.2.2 Receptor function – gas-solid interactions

As stated previously, the receptor function is the recognition of the target gas species through a physical-chemical reaction taking place at the surface of the sensitive layer and/or inside the layer of the semiconductor. The surface reaction is attributed to the exchange of free electrons between the sensitive material (adsorbent) and adsorbed gas molecules (absorbate), and the reaction in bulk is induced by the exchange between the oxygen ions of the gas and oxygen vacancies in the material. Generally, most of MOXs comprising of unstoichiometric structures as a result of oxygen deficiency causing a large number of oxygen vacancies in the volume, which is a typical property of polycrystalline materials.

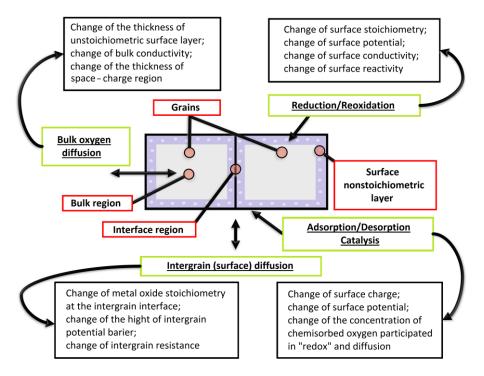

When the sensitive layer is exposed to air, the number of the molecules passing from the gaseous phase begin to cover the surface by the species of the gaseous medium. The presence of the molecules raises gas-solid interactions to occur at the grain boundaries of MOX grains. Those interactions may cause several reaction processes, which can take place at the surface, in bulk or both at the same time. It highly depends on actual conditions, as for examples, temperature, binding energy or relative pressure but also on the sensitive material form (e.g.,

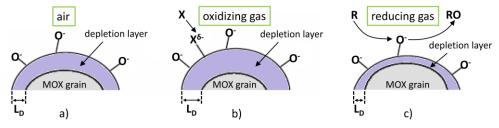

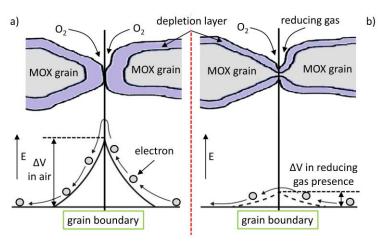

compact layer, polycrystalline structure, nanostructure). The reactions induced by gas-solid interaction generally include reduction/oxidation processes of the semiconductor, adsorption of the chemical species directly on the semiconductor and/or adsorption by reaction with surface states associated with preadsorbed ambient oxygen, the electronic transfer of delocalized conduction-band electrons to localized surface states or vice versa. Consequences of these processes for physical-chemical properties of MOXs are shown in Figure 5. [38]

Figure 5. Gas-solid interaction diagram of processes and consequences taking place in polycrystalline MOXs. Adapted from [38].

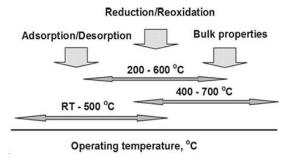

As it is shown in Figure 5, the gas sensing mechanism can go along together with several types of processes which are fundamentally different from the place of their origin. Taking into account mentioned above, before we start with a description of these processes and their mechanism, the point of our objection has to be set. This thesis devotes to the kind of MOX gas receptors, which could be easily adapted into microelectronic devices compatible with standard silicon technology. Accordingly, there are two types of MOX-based gas sensors, which differ in the region of operating temperatures, and the related detection principle in the given area.

The first, most of the commercial gas sensors (i.e., for detection hydrogen, methane or carbon oxide) operate at relatively higher temperatures about 300 - 500 °C are based on surface conduction materials considered as "surface sensors" because of the gas-solid interactions modify electron/hole density close to the surface forming chemisorbed oxygen species such as  $O_2$ -,  $O^-$  and  $O^2$ -. Here, the adsorption of oxygen at the surface and the grain boundaries leads to formations of surface oxygen ions and Schottky barriers between the grains. Those oxygen ions extract free electrons from semiconducting material and decrease its conductivity. The oxidation processes evoking different types of adsorption as a function of temperature are expressed as follows:

$$O_{2(g)} \rightarrow O_{2(ads)} \tag{1.1}$$

$$O_{2(ads)} + e^{-} \rightarrow O_{2(ads)}^{-} < 100^{\circ}C$$

(1.2)

$$O_{2(ads)}^{-} + e^{-} \rightarrow 2O_{(ads)}^{-}$$

100 < T < 300°C (1.3)

$$O_{(ads)}^{-} + e^{-} \rightarrow O_{(lattice)}^{2-} > 300^{\circ}C$$

(1.4)

The second category of gas sensors are based on bulk conduction materials so-called "bulk defect sensors," for example,  $Ga_2O_3$  and  $SrTiO_3$ . They are operating at higher temperatures about  $700-1100\,^{\circ}C$ , taking advantage of natural nonstoichiometry of semiconducting oxide, where oxygen vacancies diffuse quickly from the interior of the grains to the surface, or from the surface to the interior of the grains. Here, as an example can be a lambda sensor used in an internal combustion engine that controls the air-to-fuel A/F ratio. [43,44]

Figure 6. Processes controlling response of high temperature and low-temperature MOX gas sensors [45].

In principle, in the case of surface sensors due to a small constant of bulk oxygen diffusion the chemical composition of the material does not reach an equilibrium state during the time of gas detection. It is a so-called redox mechanism, reduction/reoxidation respectively. At still lower temperatures, the adsorption/desorption processes (chemisorption) can dominate in surface reactions as it is shown in Figure 6 [45,46]. On the contrary, the sensing mechanism of high temperature operating bulk defect sensors is based on bulk oxygen diffusion, when the absorption/desorption mechanism is suppressed. Both sensors have its advantages and disadvantages, but it is necessary to note that bulk defect sensors require, very often, high demands on the robust heating system, which is not in line with semiconductor technologies [38]. Therefore, we will only focus on the mechanisms that apply to the surface sensors, concerning catalytic reactions such as adsorption/desorption.

### Adsorption and desorption mechanism

Iwamoto [47] investigated the adsorption mechanism of oxygen on MOXs by using a TPD (Temperature Programmed Desorption) technique about 40 years ago. Adsorption can be described as an increase in the concentration of a dissolved substance at the interface of a condensed and a gaseous phase due to the effect of surface forces. Focusing on the sticking of gas molecules (adsorbate) at a solid surface (adsorbent), we can describe the flux of molecules impinging a surface ( $\phi_i$ ), by the Hertz-Knudsen equation [48]:

$$\phi_i = \frac{p}{(2 \cdot \pi \cdot m \cdot k_B \cdot T)^{\frac{1}{2}}} \tag{1.5}$$

where p is the pressure, m the mass of the molecule,  $k_B$  the Boltzmann constant and T the temperature. When molecules are in contact with the surface, they can be adsorbed and later desorbed. This sorption process depends on several factors as the actual operational temperature, the binding energy with the surface or pressure. There are two types of adsorption, which differ in the diverse forces that retain the adsorbed molecules on the surface. In other words, the forces that arise between a solid and a foreign molecule can be of different nature. Thus, if the forces of action have a physical nature, there is *physical adsorption* (physisorption) that extends over the entire surface, where the interaction takes place without involving charge transfer between the adsorbent and adsorbate. In principle, it is assumed that the surface of the solid follows an unspecific interaction with the adsorbate, i.e., the interaction takes places on all surface sites with the molecule independently of the gas species, attracting the molecule due to Van der Waals's interactive forces or electrostatic polarization forces as long as the proper pressure and temperature conditions are kept [49]. Van der Waals interactive forces induce a long-range interaction, which attracts the gas molecule for a purpose to minimize its energy. The interaction involves small adsorption energy, up to 0.01 - 0.1 eV [50]. Due to the low binding energy, the physisorbed particles are highly mobile on the surface and are easily desorbed. This process is reversible, non-activated and non-dissociative, i.e., the gas species remains unmodified, and takes place usually at temperatures close to their boiling point. At higher temperatures, the physisorption can be neglected.

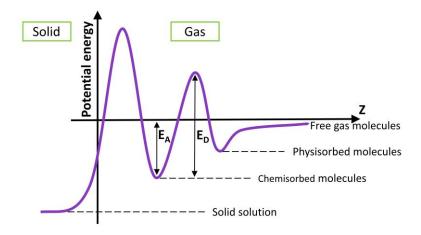

The second type of adsorption deals with the forces adsorption processes that involve a chemical nature. This type of interactions takes place for higher adsorption energies, where electrons are shared between the gas adsorbate and solid adsorbent, which gives rise to *chemical adsorption*. The interaction energy during the chemisorption of adsorbates may reach several eV, approximately one order of magnitude above the characteristic values for physisorption. Although the effectiveness of the chemisorption may be limited to a specific temperature range, chemisorption has no restrictions on temperature, unlike physisorption. For instance, physisorption phenomena prevail due to slow chemisorption mechanism, which barely takes place at low temperatures (e.g., at room temperature). It is known as non-activated chemisorption process. The activated chemisorption requires additional energy (activation energy) in order to pass from physisorbed stated to the chemisorbed state. The additional energy is mostly achieved by raising the temperature. Figure 7 depicts a typical adsorption curve, representing the potential energy of the system as a function of the distance *z* between the absorbent solid surface and the gas molecule being adsorbed.

Figure 7. The energy of a gas molecule at a solid-gas interface.  $E_A$ : adsorption energy,  $E_D$ : desorption energy. Adapted from [51].

If the intersection between physisorption and chemisorption energy get negative values, the process calls as non-activated, when the intersection occurs at positive values it is activated chemisorption, respectively. Usually, chemisorption is activated adsorption, but the presence of activation energy is not necessarily a criterion of chemisorption in some cases, e.g., the adsorption of common gases such as  $H_2$ , CO or  $N_2$ , where there is no activation energy or the difference  $E_A$ - $E_D$  is negligibly small. [49]

In summary, the adsorption of gas molecules on solid surfaces can lead to the following events [52]:

- a. the molecule loses some energy transferring it to the solid and reaching the physical adsorbed state (i.e., translational energy),

- b. the gas molecule is scattered by the surface in an elastic process, without any loss of energy,

- c. the molecule passes, if the energy is high enough, directly to a chemisorbed state if this can be formed near the incidence site, without being trapped in the physically adsorbed state,

- d. within the formation of the chemically adsorbed species, the molecule or its dissociated parts can lose chemical energy (released to the solid, and become localized at the original site) or lose energy and hop diffusively until the excess of energy is dissipated,

- e. the molecule can be physisorbed at the site of the incidence, then it may be chemisorbed, be inelastically scattered back to the gas phase or hop to a neighboring site, where can take place cases a) and b).

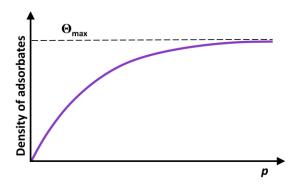

Generally speaking, the adsorption and desorption mechanism during gas-solid interactions may be qualitatively described by adsorption isotherm or isobar. The dependence of the adsorbed amount of the gas on its partial pressure at a constant temperature is called as adsorption isotherm. On the contrary, the dependence of the adsorbed amount of the gas on a

certain temperature at constant pressure is adsorption isobar. In the case of adsorption isotherm, at a constant temperature, the adsorbed amount of the gas increases with the pressure or vice versa, the adsorbed amount increases with temperature at constant pressure when we are talking about adsorption isobar, respectively.

While the qualitative description gives us only a general idea of ongoing events, the mechanism of gas-solid interaction is quantitatively better described with several conventional models. For instance, the energy potential of chemisorption can be represented as a Lennard-Jones potential, Buckingham potential or Morse potential [53]. These models allow for the analysis of the gas interactions at the surface of the sensitive layer at constant pressure and different temperature (adsorption isobars). The Lennard-Jones model of activation barriers is most commonly applied between the physisorbed and chemisorbed states.

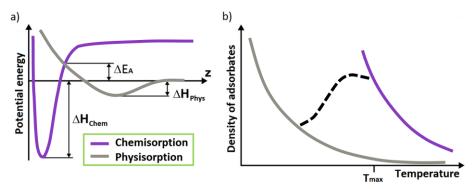

Figure 8a shows the dependence of the desorption activation energy barrier  $\Delta E_A$  of neutral molecules on the distance z, which is the distance that needs to be overcome for a physisorbed molecule to reach the chemisorption well. Typical adsorption isobars are depicted in Figure 8b, where the solid lines represent the equilibrium physisorption and a chemisorption isobar, the dashed line represents irreversible chemisorption. Maximum coverage of chemisorbed molecules is obtainable at the temperature  $T_{max}$ ; below this temperature, the chemisorption is irreversible because the rate of desorption becomes negligible. [54]

Figure 8. Lennard-Jones model for physisorption and chemisorption of a molecule. Adapted from [54].

Adsorption is always an exothermic reaction; it means that the level of adsorbed quantity at constant pressure will decrease with increasing temperature. At low temperatures, the molecules are captured in a physical state because they cannot overcome the activation barrier  $\Delta E_A$ , which also corresponds to the maximum coverage at  $T_{max}$ .

Accordingly, to the Lennard-Jones activation energy model, the rate of chemisorption  $d\Theta/dt$  is given by the difference between the adsorption and desorption rate:

$$\frac{d\Theta}{dt} = k_{ads} \cdot exp\left[-\frac{\Delta E_A}{k_B \cdot T}\right] - k_{des} \cdot \Theta \cdot exp\left\{-\frac{(\Delta E_A + \Delta H_{Chem})}{k_B \cdot T}\right\}$$

(1.6)

where  $\Theta$  is the proportion of unoccupied surface with chemisorbed particles,  $k_{ads}$  and  $k_{des}$  are rate constants for adsorption and desorption,  $\Delta E_A$  is the activation barrier for desorption, and  $\Delta H_{Chem}$  is the reaction heat of chemisorption [55]. Considering the equilibrium conditions

dH/dt = 0, then the rate of adsorption will be equal to desorption rate, and the coverage density  $\Theta$  depends on the reaction heat of chemisorption  $\Delta H_{Chem}$  and can be expressed as:

$$\Theta = \frac{k_{ads}}{k_{des}} \cdot exp\left(-\frac{\Delta H_{Chem}}{k_B \cdot T}\right) \tag{1.7}$$

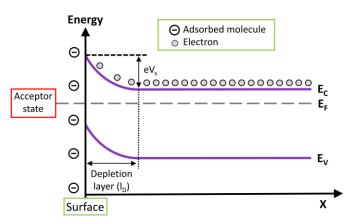

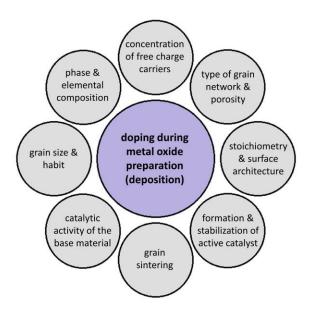

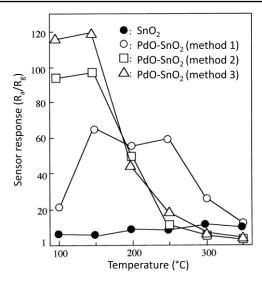

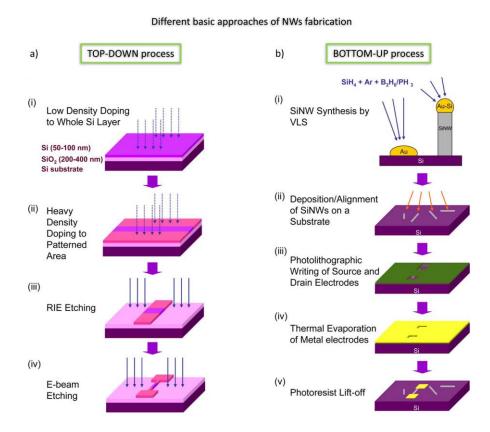

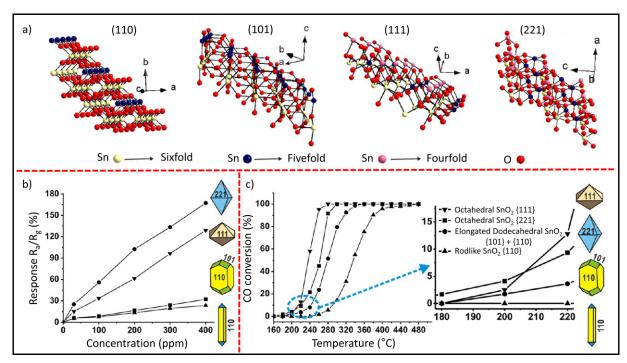

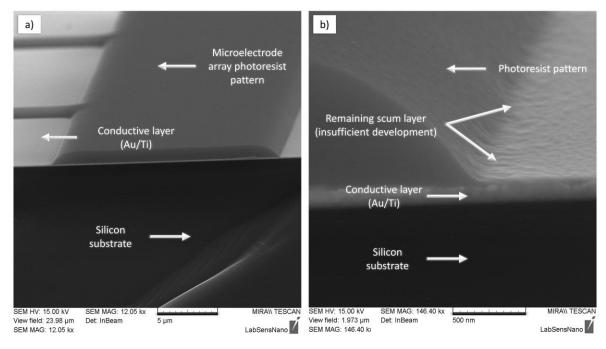

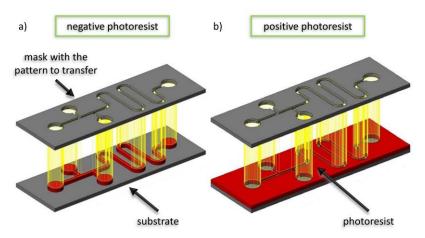

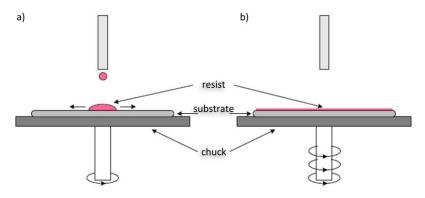

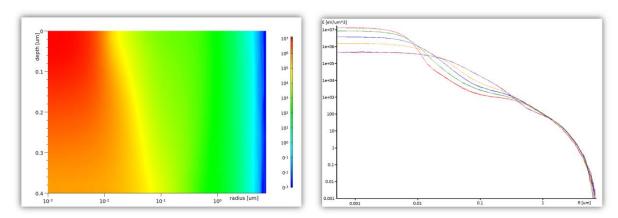

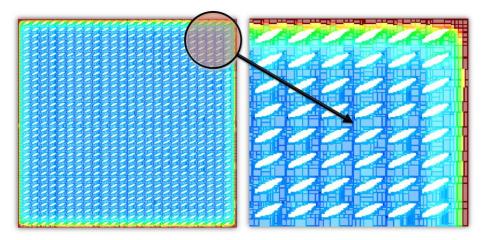

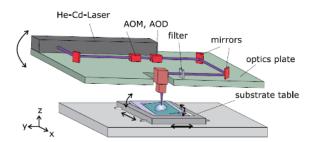

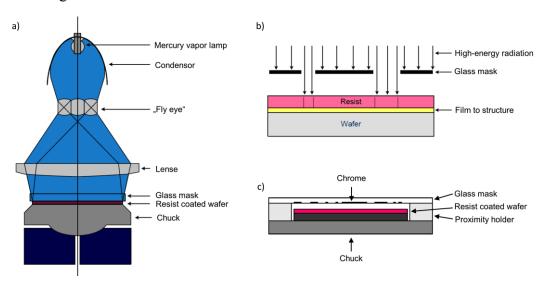

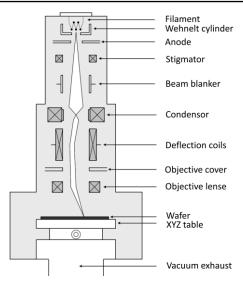

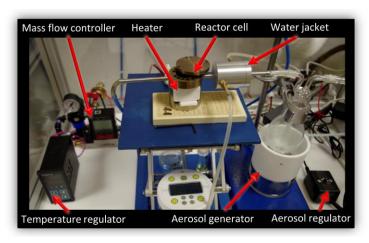

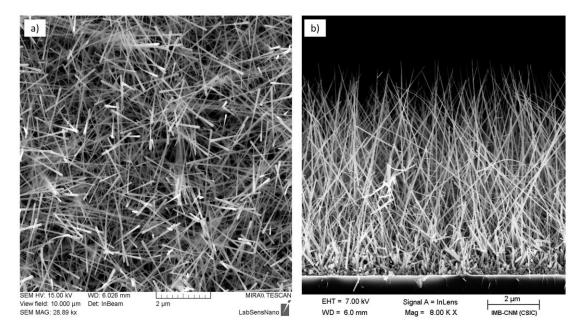

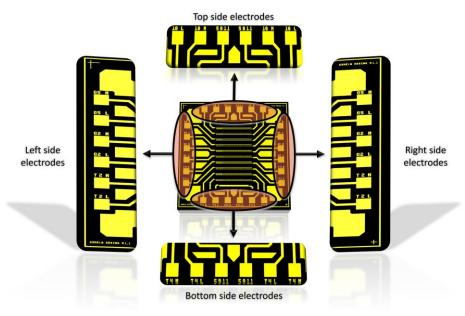

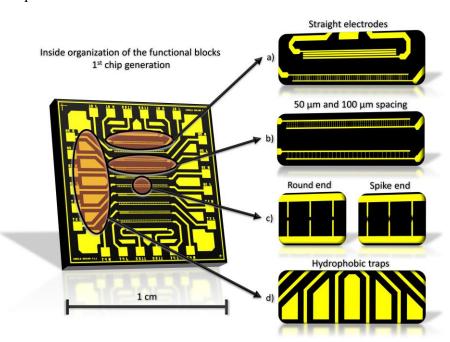

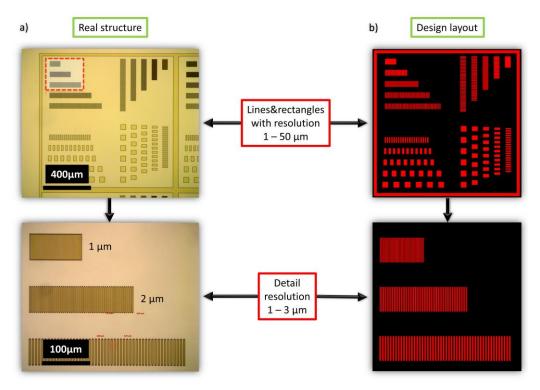

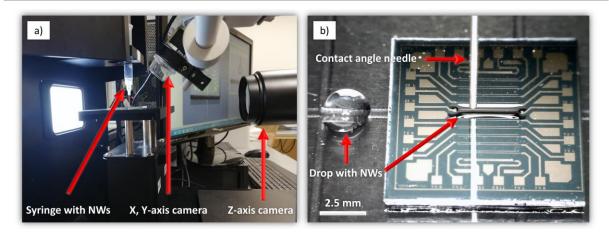

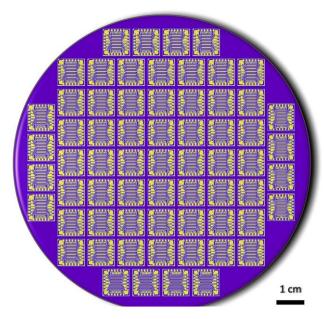

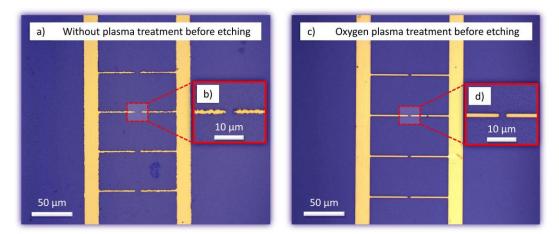

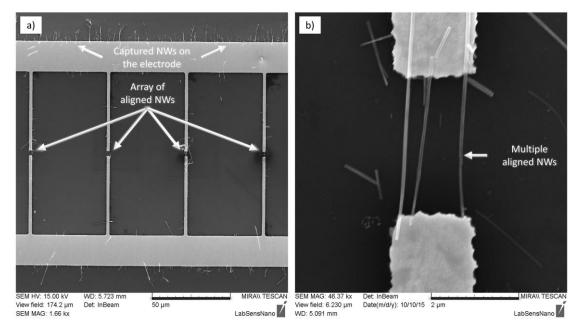

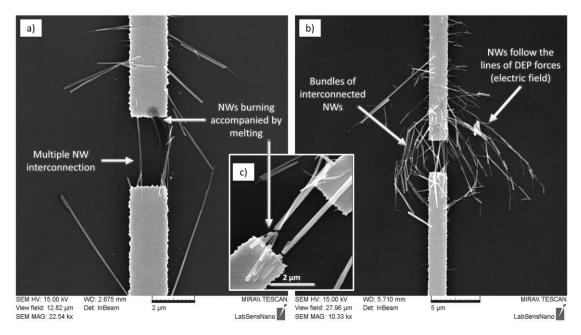

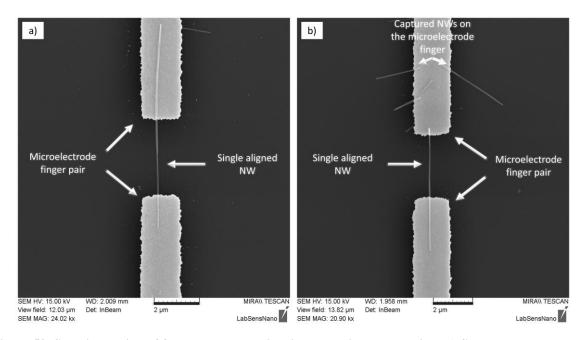

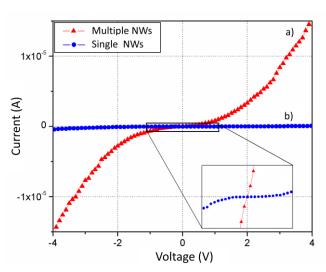

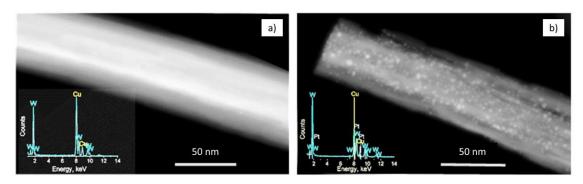

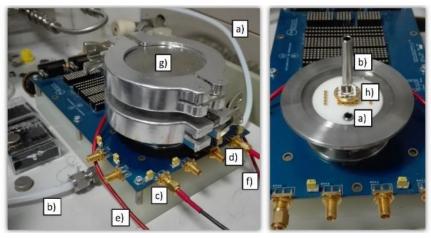

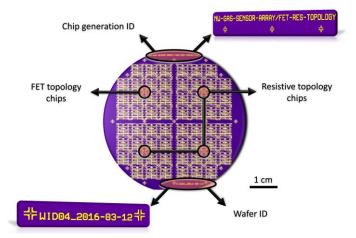

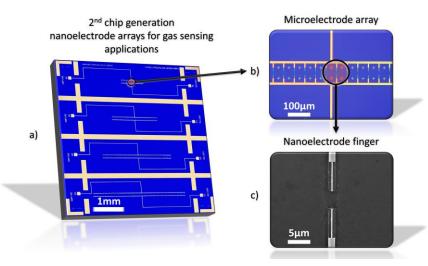

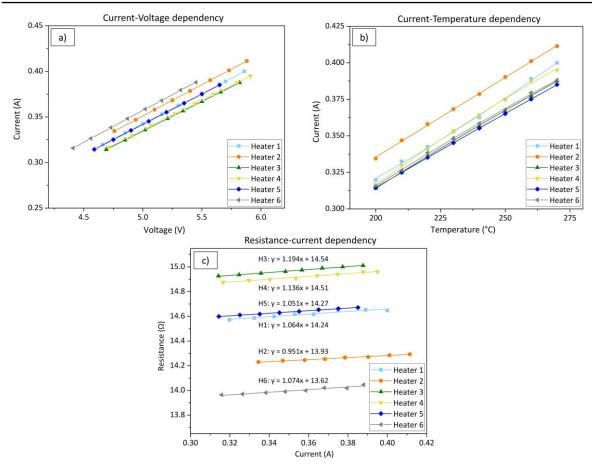

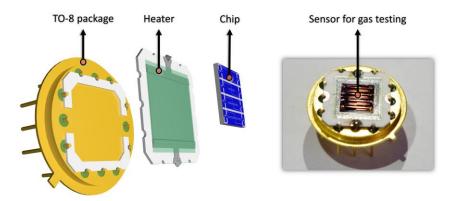

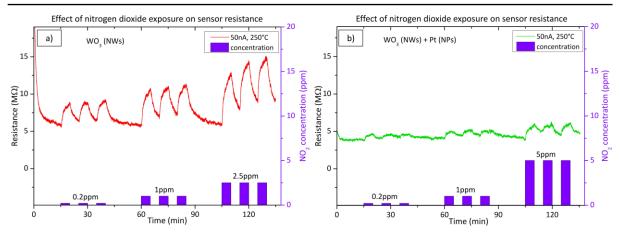

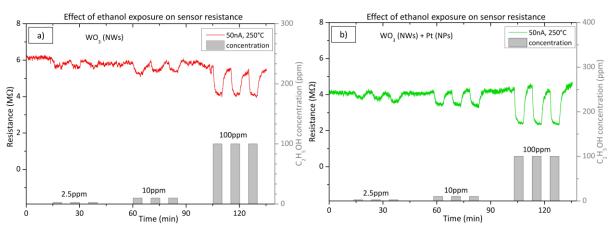

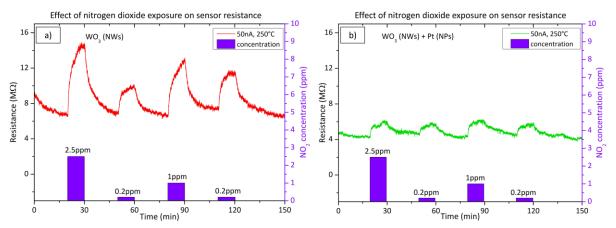

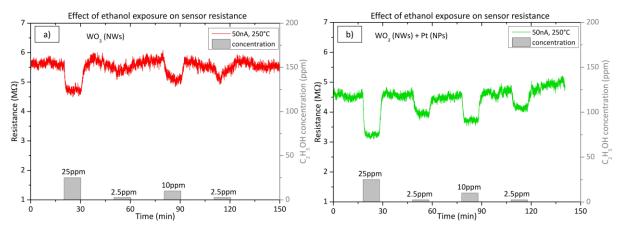

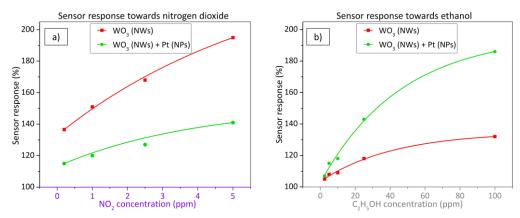

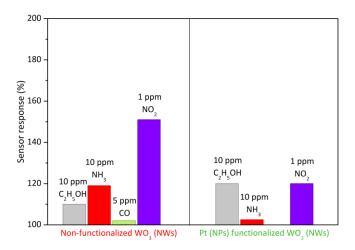

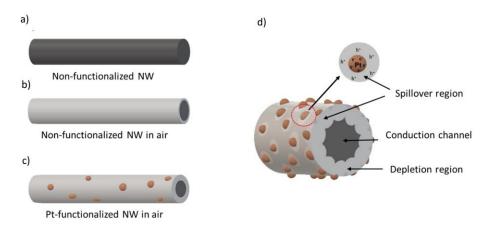

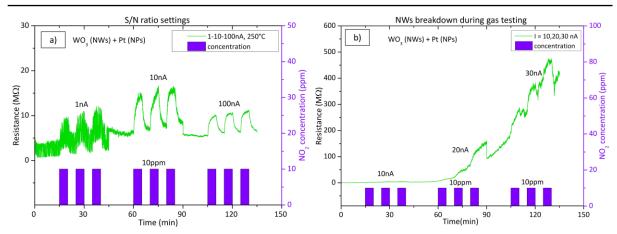

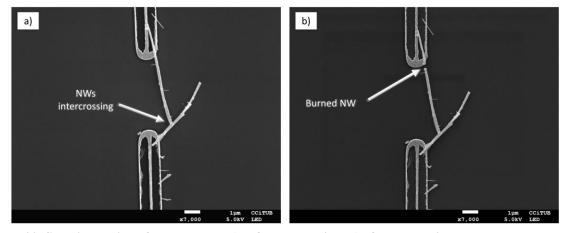

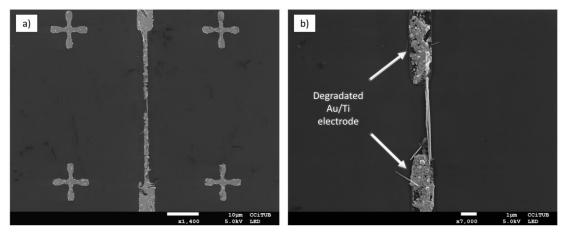

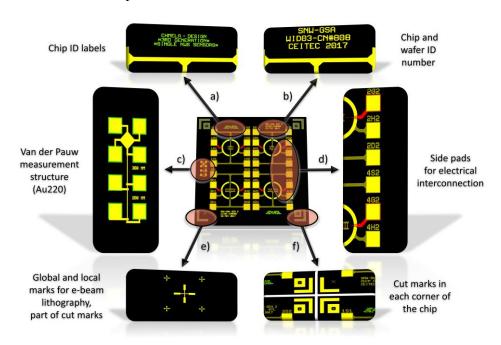

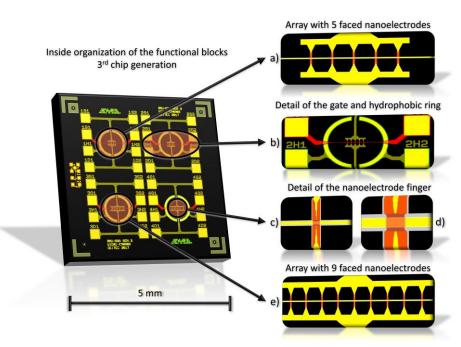

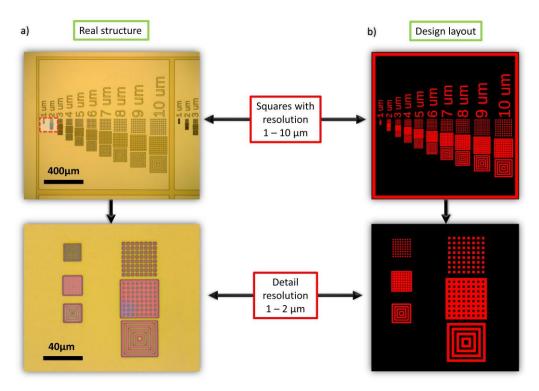

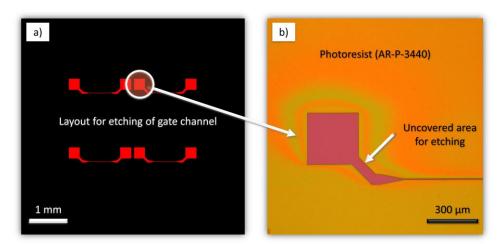

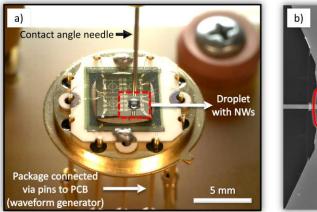

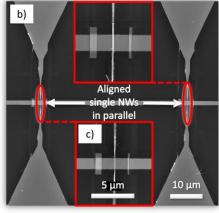

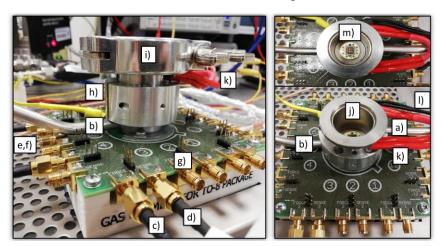

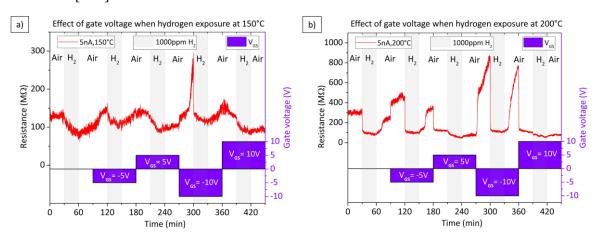

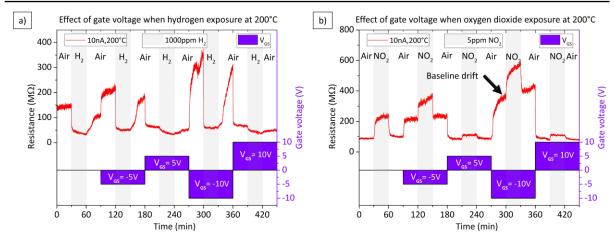

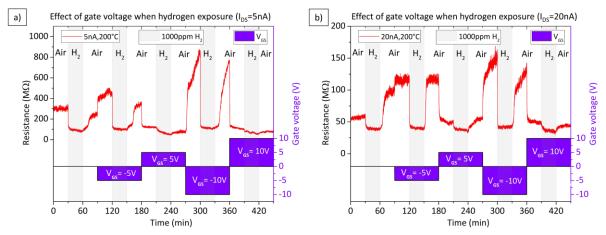

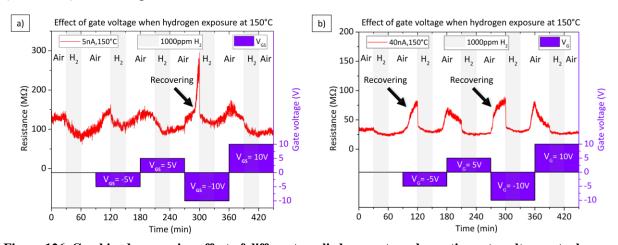

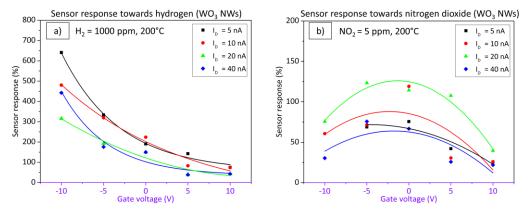

Even though Lennard-Jones potential is a simple mathematical model which approximate the interaction between a pair of neutral atoms or molecules, it has to be mentioned that it is largely simplifying and omit some of the phenomena that may occur. Among them the site availability and repulsive forces between the adsorbed molecules, and the dependence of  $\Delta H_{Chem}$  on the level of surface coverage. Also, the charging heat required for adsorption is not included in the model. In the case of ionosorption, the adsorption heat is related to the acceptor level in the molecule and the electrochemical potential of the electrons (Fermi level) of the solid material. Due to the negative surface charge of a higher energy level in the solid, the energy distance between the acceptor level and Fermi energy is also reduced that leads to the reduction of adsorption heat. Thus, with a subsequent increase of surface coverage, the adsorption heat further decrease. Apart from the adsorption heat, the activation barrier for chemisorption also changes with the concentration of molecules on the surface. [56]